# **Magellan® Motion Control IC**

# MC58000 Electrical Specifications

Revision 2.7/ January 2024

Performance Motion Devices, Inc.

80 Central Street, Boxborough, MA 01719

www.pmdcorp.com

### NOTICE

This document contains proprietary and confidential information of Performance Motion Devices, Inc., and is protected by federal copyright law. The contents of this document may not be disclosed to third parties, translated, copied, or duplicated in any form, in whole or in part, without the express written permission of PMD.

The information contained in this document is subject to change without notice. No part of this document may be reproduced or transmitted in any form, by any means, electronic or mechanical, for any purpose, without the express written permission of PMD.

Copyright 1998–2024 by Performance Motion Devices, Inc.

Juno, Atlas, Magellan, ION, Prodigy, Pro-Motion, C-Motion and VB-Motion are trademarks of Performance Motion Devices, Inc.

### Warranty

Performance Motion Devices, Inc. warrants that its products shall substantially comply with the specifications applicable at the time of sale, provided that this warranty does not extend to any use of any Performance Motion Devices, Inc. product in an Unauthorized Application (as defined below). Except as specifically provided in this paragraph, each Performance Motion Devices, Inc. product is provided "as is" and without warranty of any type, including without limitation implied warranties of merchantability and fitness for any particular purpose.

Performance Motion Devices, Inc. reserves the right to modify its products, and to discontinue any product or service, without notice and advises customers to obtain the latest version of relevant information (including without limitation product specifications) before placing orders to verify the performance capabilities of the products being purchased. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement and limitation of liability.

### **Unauthorized Applications**

Performance Motion Devices, Inc. products are not designed, approved or warranted for use in any application where failure of the Performance Motion Devices, Inc. product could result in death, personal injury or significant property or environmental damage (each, an "Unauthorized Application"). By way of example and not limitation, a life support system, an aircraft control system and a motor vehicle control system would all be considered "Unauthorized Applications" and use of a Performance Motion Devices, Inc. product in such a system would not be warranted or approved by Performance Motion Devices, Inc.

By using any Performance Motion Devices, Inc. product in connection with an Unauthorized Application, the customer agrees to defend, indemnify and hold harmless Performance Motion Devices, Inc., its officers, directors, employees and agents, from and against any and all claims, losses, liabilities, damages, costs and expenses, including without limitation reasonable attorneys' fees, (collectively, "Damages") arising out of or relating to such use, including without limitation any Damages arising out of the Performance Motion Devices, Inc. product to conform to specifications.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent procedural hazards.

### Disclaimer

Performance Motion Devices, Inc. assumes no liability for applications assistance or customer product design. Performance Motion Devices, Inc. does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of Performance Motion Devices, Inc. covering or relating to any combination, machine, or process in which such products or services might be or are used. Performance Motion Devices, Inc.'s publication of information regarding any third party's products or services does not constitute Performance Motion Devices, Inc.'s approval, warranty or endorsement thereof.

### Patents

Performance Motion Devices, Inc. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Patents and/or pending patent applications of Performance Motion Devices, Inc. are listed at https://www.pmdcorp.com/company/patents.

### **Related Documents**

#### Magellan® Motion Control IC User Guide

Complete description of the Magellan Motion Control IC features and functions with detailed theory of operation.

#### **C-Motion Magellan Programming Reference**

Descriptions of all Magellan Motion Control IC commands, with coding syntax and examples, listed alphabetically for quick reference.

### DK58420 Developer Kit User Manual

How to install and configure the DK58420 and DK55420 developer kits.

#### Atlas Digital Amplifier User Manual

Description of the Atlas Digital Amplifier electrical and mechanical specifications along with a summary of its operational features.

### Atlas Digital Amplifier Complete Technical Reference

Complete technical and mechanical description of the Atlas Digital Amplifier with detailed theory of operations.

## **Table of Contents**

| 1.1<br>1.2                       | The MC50000 Family9Magellan Motion Control IC Family Overview9MC58420-Series ICs & Developer Kit10                                                                                                                                                |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2.</b> 1<br>2.2<br>2.3<br>2.4 | Functional Characteristics13Configurations, Parameters, and Performance.13Physical Characteristics and Mounting Dimensions.15Absolute Maximum Environmental and Electrical Ratings17MC58110 System Configuration — Single Chip, 1 Axis Control.17 |

| 2.5                              | MC58x20 System Configuration — Two Chip, 1 to 4 Axis Control 19                                                                                                                                                                                   |

| <b>3.</b><br>3.1                 | Electrical Characteristics         21           DC Characteristics for 58110, 58x20 CP.         21                                                                                                                                                |

| 3.1<br>3.2<br>3.3                | DC Characteristics for 58x20 IO                                                                                                                                                                                                                   |

| 4.                               | I/O Timing Diagrams                                                                                                                                                                                                                               |

| 4.1                              | Clock                                                                                                                                                                                                                                             |

| 4.2                              | Quadrature Encoder Input                                                                                                                                                                                                                          |

| 4.3<br>4.4                       | Reset         26           Host Interface, 8/16 Mode         27                                                                                                                                                                                   |

| 4.4<br>4.5                       | Host Interface, 16/16 Mode                                                                                                                                                                                                                        |

| 4.5                              | External Memory Timing                                                                                                                                                                                                                            |

| 4.7                              | Peripheral Device Timing                                                                                                                                                                                                                          |

| 4.8                              | SPI DAC Timing                                                                                                                                                                                                                                    |

| 4.9                              | SPI Atlas Timing                                                                                                                                                                                                                                  |

| 5.                               | Pinouts and Pin Descriptions                                                                                                                                                                                                                      |

| 5.1                              | Pinouts for the MC58110                                                                                                                                                                                                                           |

| 5.2                              | MC58110 Pin Descriptions                                                                                                                                                                                                                          |

| 5.3                              | Pinouts for the MC58x20                                                                                                                                                                                                                           |

| 5.4                              | MC58x20 Pin Descriptions                                                                                                                                                                                                                          |

| 6.                               | Application Notes — MC58110 and MC58x20                                                                                                                                                                                                           |

| 6.1                              | General Design Notes                                                                                                                                                                                                                              |

| 6.2                              | Peripheral Device Access                                                                                                                                                                                                                          |

| 6.3                              | Power Supplies                                                                                                                                                                                                                                    |

| 6.4                              | Clock Generator, Grounding and Decoupling, and Device Reset                                                                                                                                                                                       |

| 6.5                              | Serial Communication Interface (SCI)                                                                                                                                                                                                              |

| 6.6                              | CAN Communication Interface                                                                                                                                                                                                                       |

| 6.7                              | External Memory                                                                                                                                                                                                                                   |

| 6.8                              | Asynchronous SRAM                                                                                                                                                                                                                                 |

| 6.9                              | Using the On-chip ADC                                                                                                                                                                                                                             |

| 6.10<br>6.11                     | •                                                                                                                                                                                                                                                 |

| 6.12                             | ·                                                                                                                                                                                                                                                 |

| 6.13                             |                                                                                                                                                                                                                                                   |

| 6.14                             |                                                                                                                                                                                                                                                   |

| 6.15                             |                                                                                                                                                                                                                                                   |

| 6.16 | Single-Axis Magellan with Brushless DC Atlas                  |

|------|---------------------------------------------------------------|

|      | Multi-Axis Magellan with DC Brush & Step Motor Atlas          |

|      | Pulse & Direction Mode Output Connected to Atlas              |

|      | Using PWM for DC Brush, Brushless DC and Microstepping Motors |

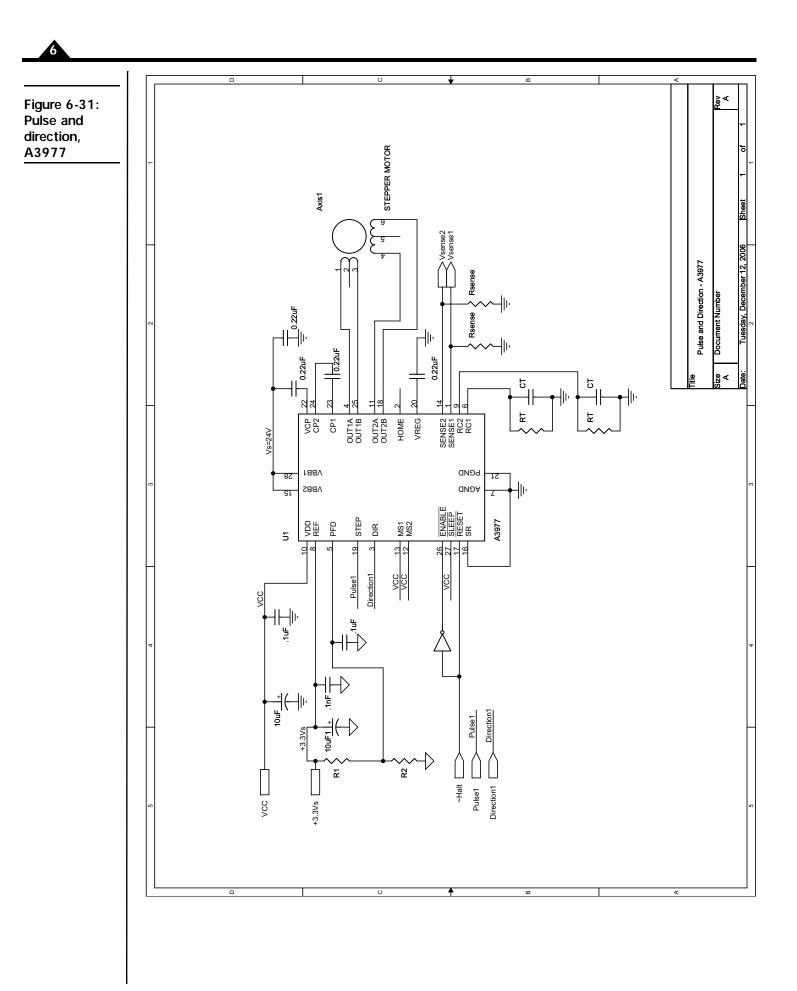

|      | Using the Allegro A3977 to Drive Microstepping Motors         |

# **List of Figures**

| 1 1        | DK58420 Board                                      |

|------------|----------------------------------------------------|

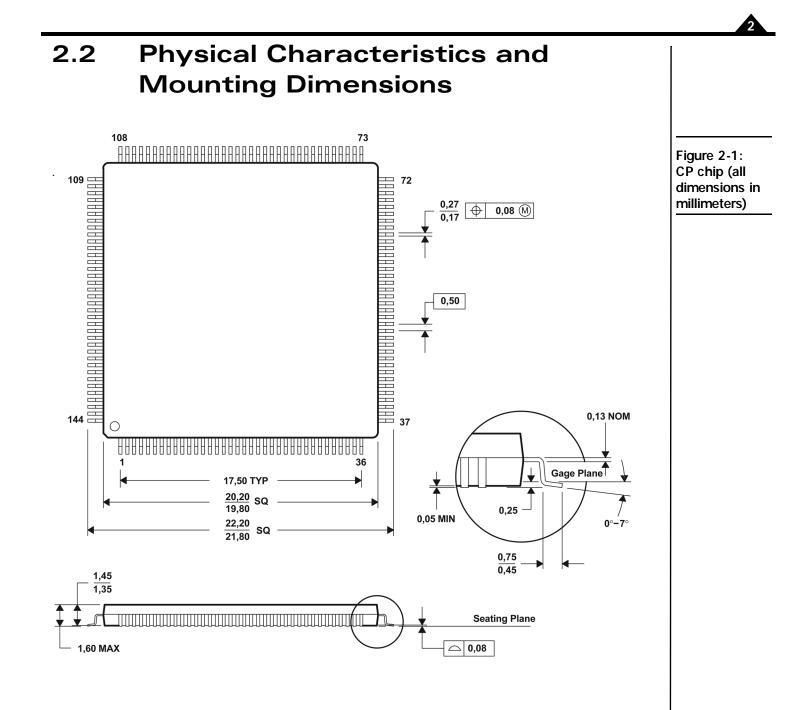

| 1-1<br>2-1 | CP chip (all dimensions in millimeters)            |

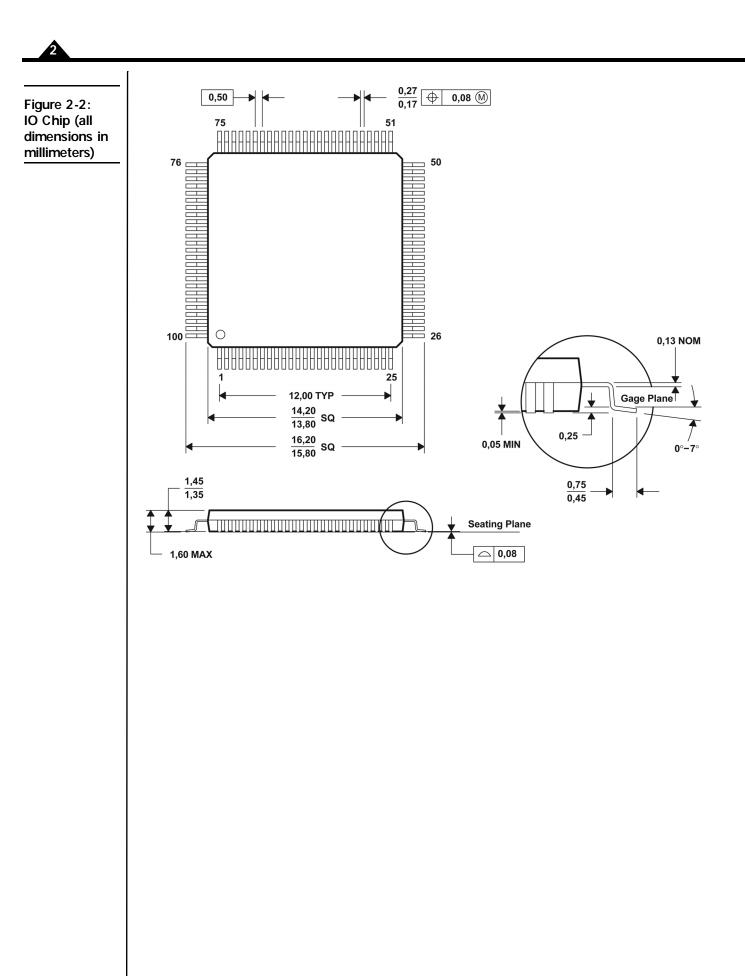

| 2-1<br>2-2 | IO Chip (all dimensions in millimeters)            |

| 2-2<br>2-3 | •                                                  |

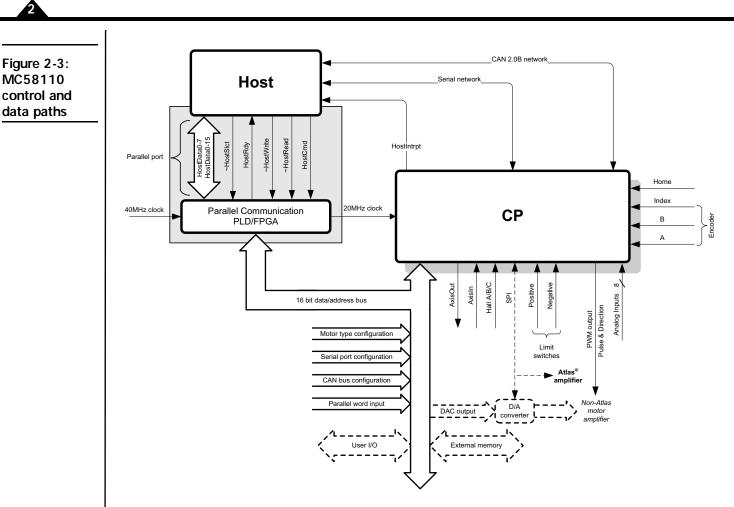

|            | MC58110 control and data paths                     |

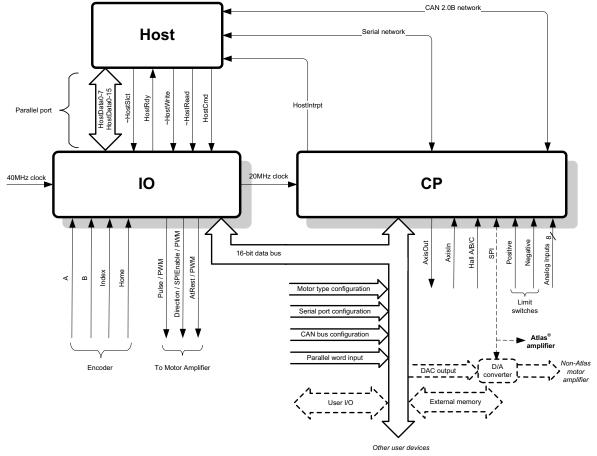

| 2-4        | MC58x20 control and data paths                     |

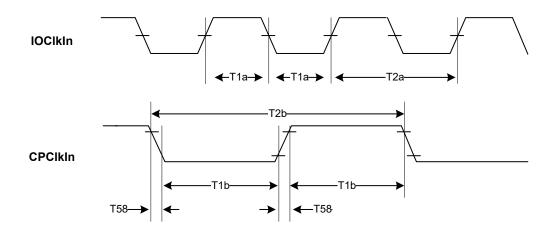

| 4-1        | Clock timing                                       |

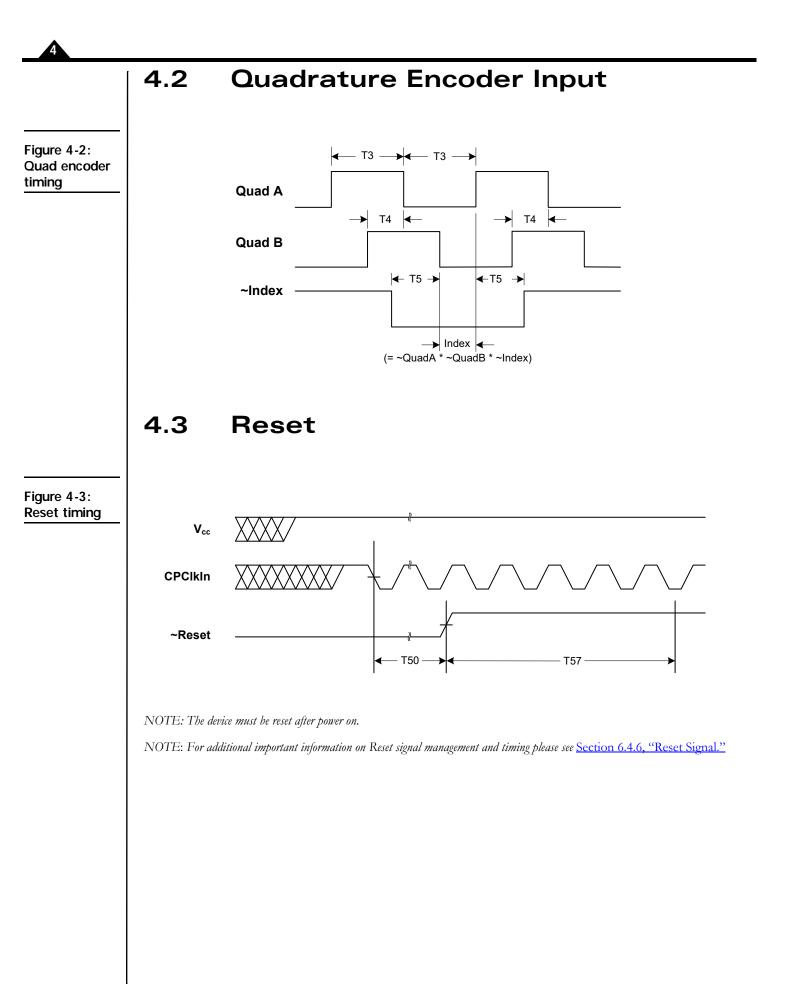

| 4-2        | Quad encoder timing                                |

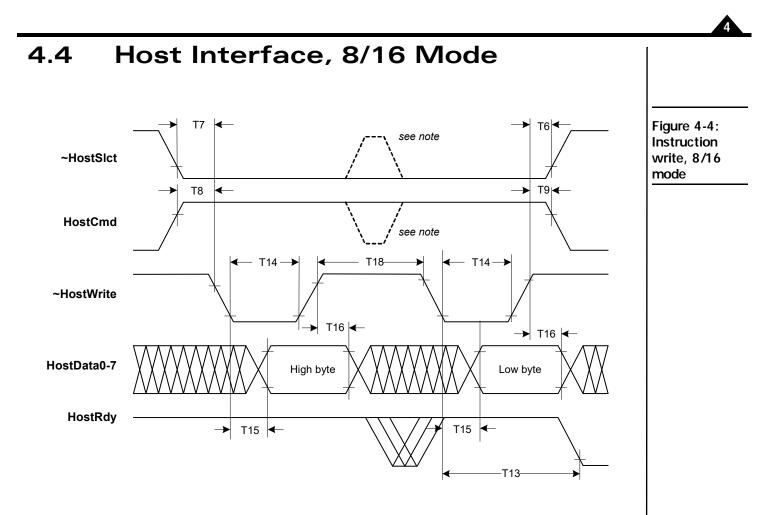

| 4-3        | Reset timing                                       |

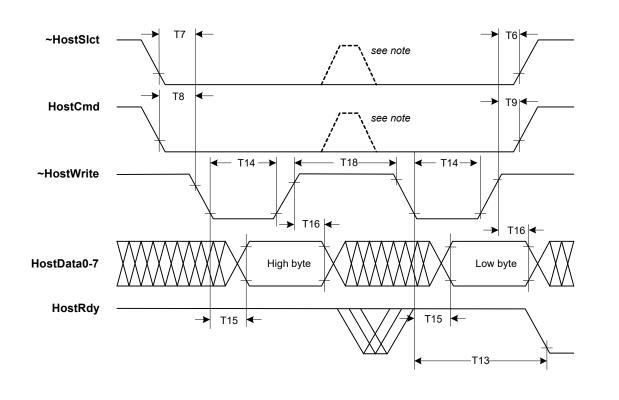

| 4-4        | Instruction write, 8/16 mode                       |

| 4-5        | Data write, 8/16 mode                              |

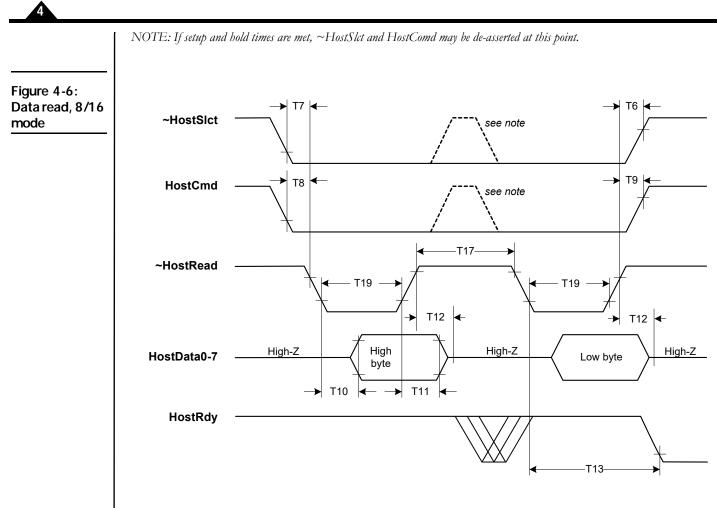

| 4-6        | Data read, 8/16 mode                               |

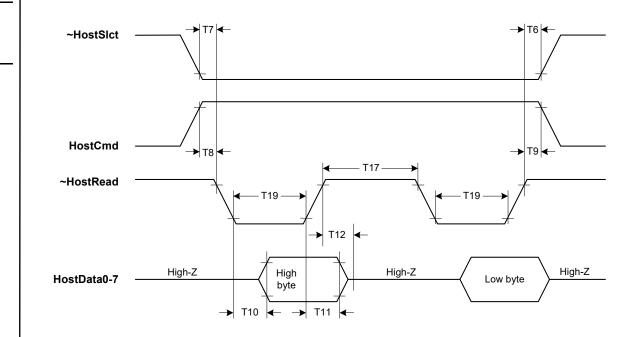

| 4-7        | Status read, 8/16 mode                             |

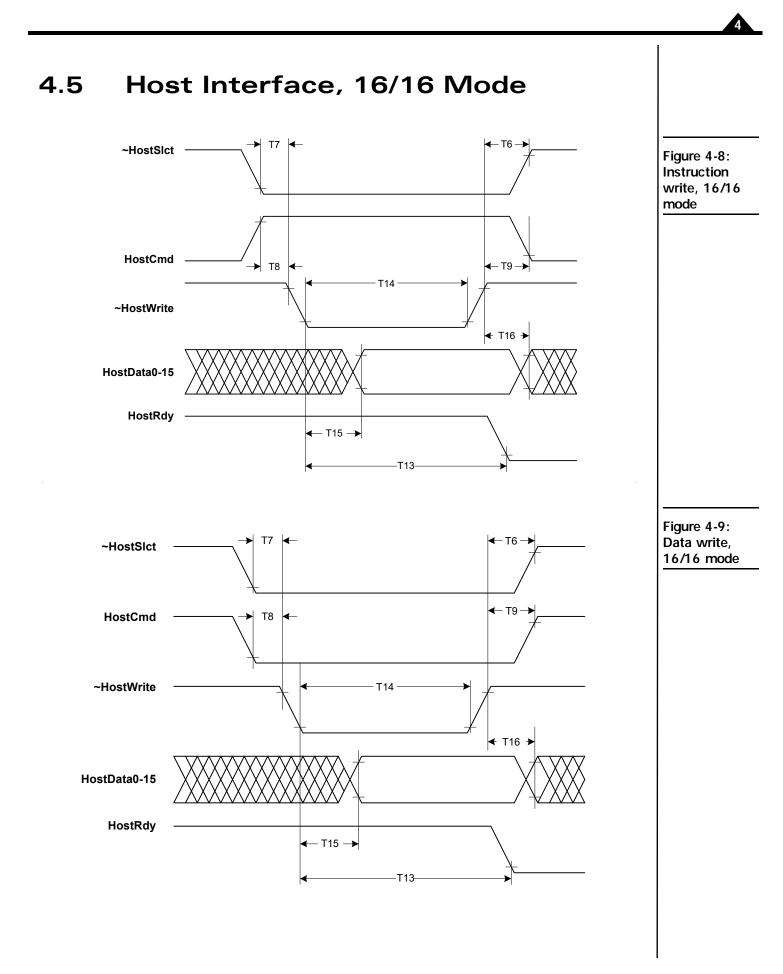

| 4-8        | Instruction write, 16/16 mode                      |

| 4-9        | Data write, 16/16 mode                             |

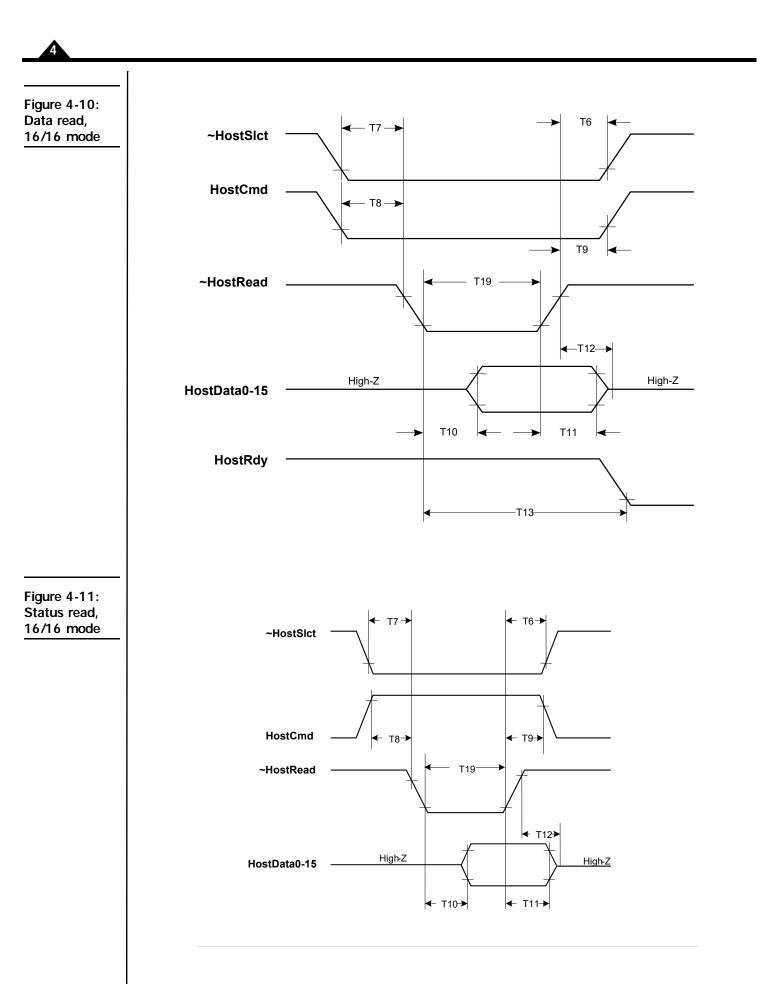

| 4-10       | Data read, 16/16 mode                              |

| 4-11       | Status read, 16/16 mode                            |

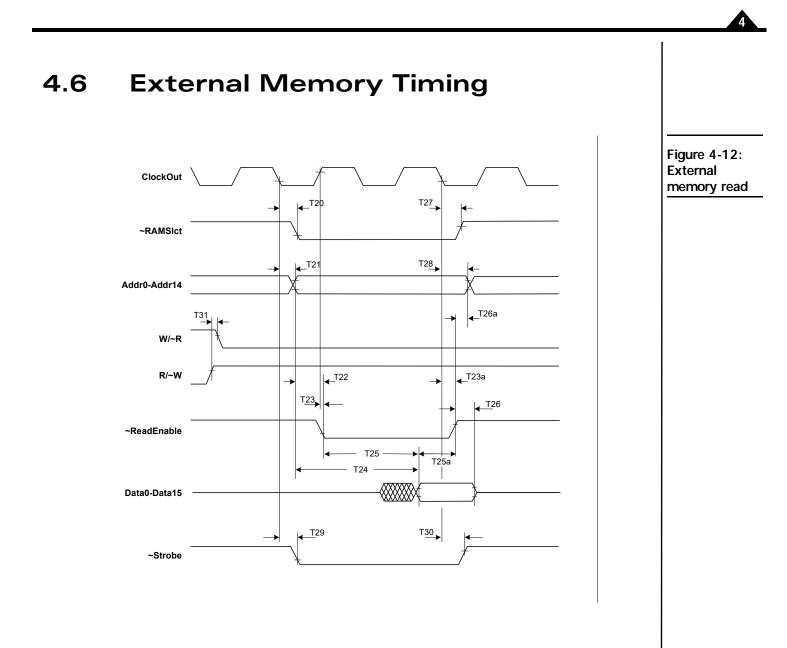

| 4-12       | External memory read                               |

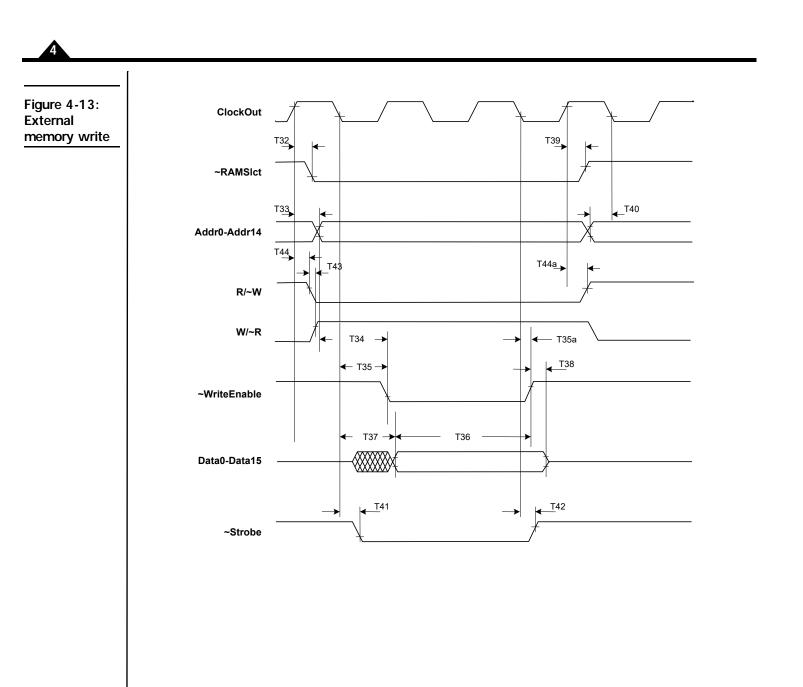

| 4-13       | External memory write                              |

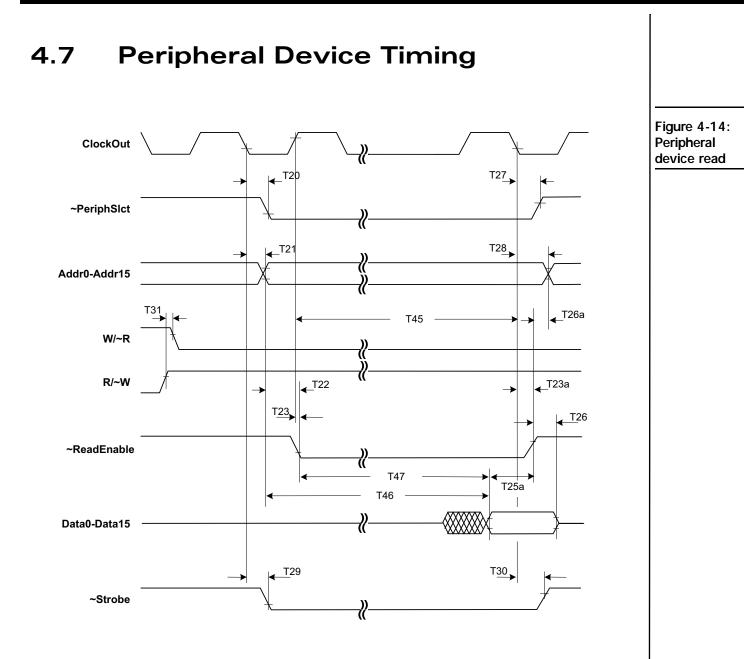

| 4-14       | Peripheral device read                             |

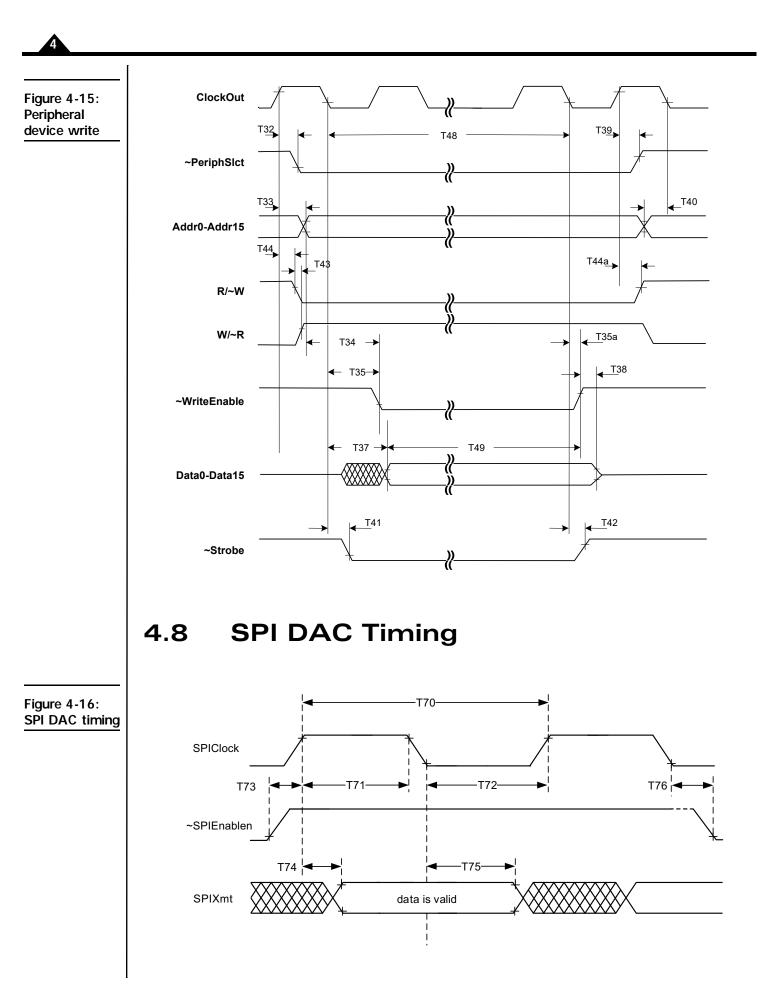

| 4-15       | Peripheral device write                            |

| 4-16       | SPI DAC timing                                     |

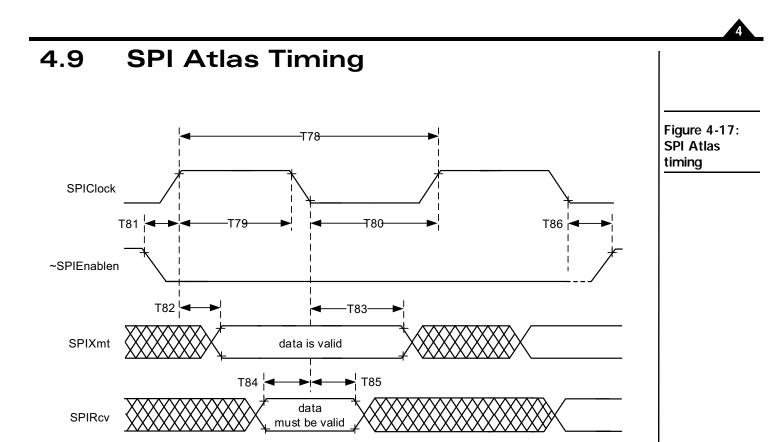

| 4-17       | SPI Atlas timing                                   |

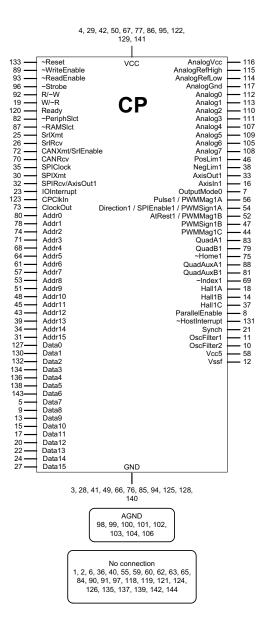

| 5-1        | MC58110 pinouts                                    |

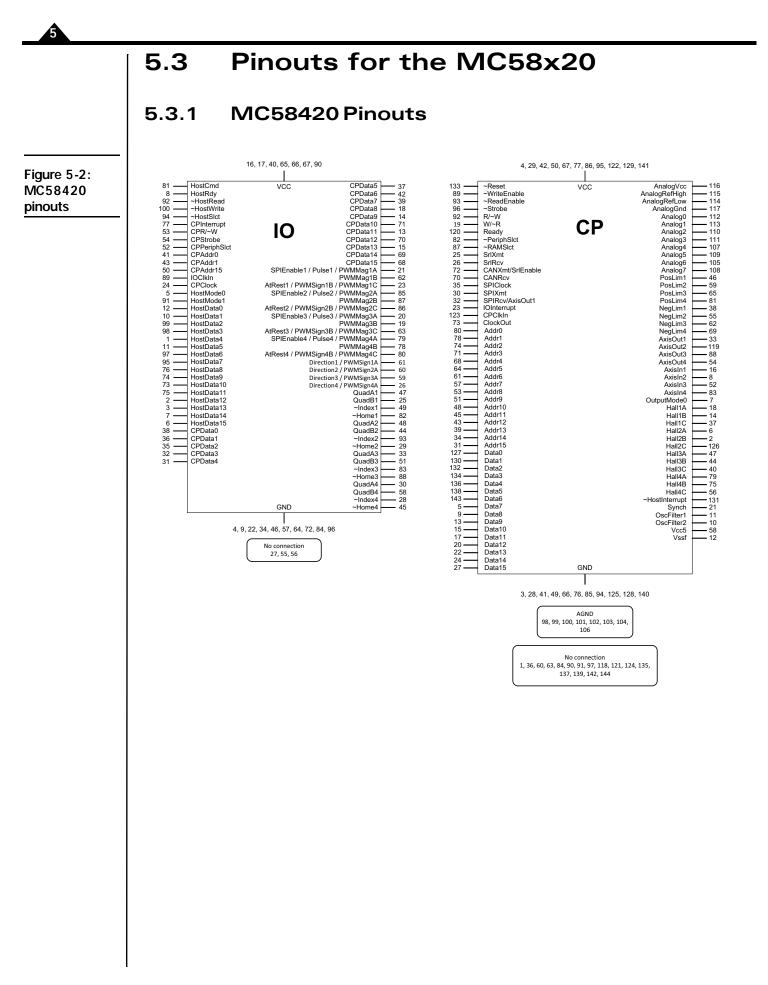

| 5-2        | MC58420 pinouts                                    |

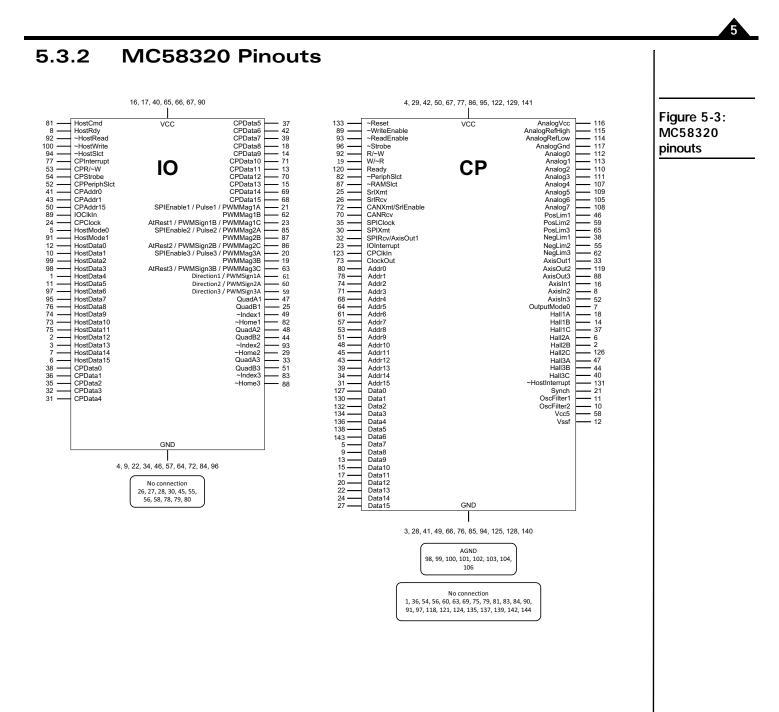

| 5-3        | MC58320 pinouts                                    |

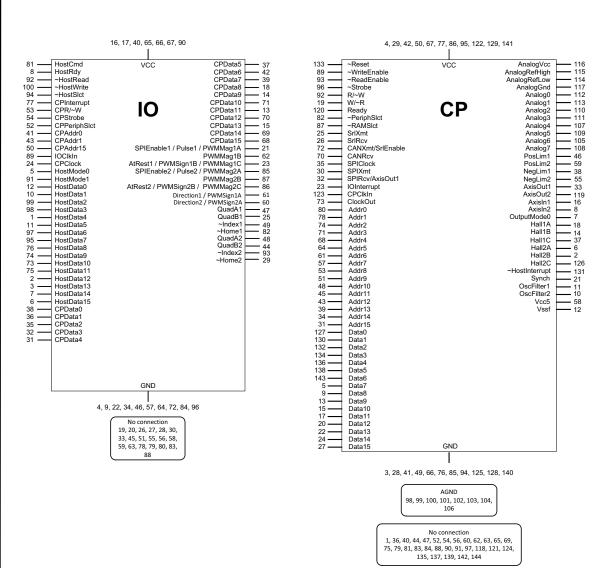

| 5-4        | MC58220 pinouts                                    |

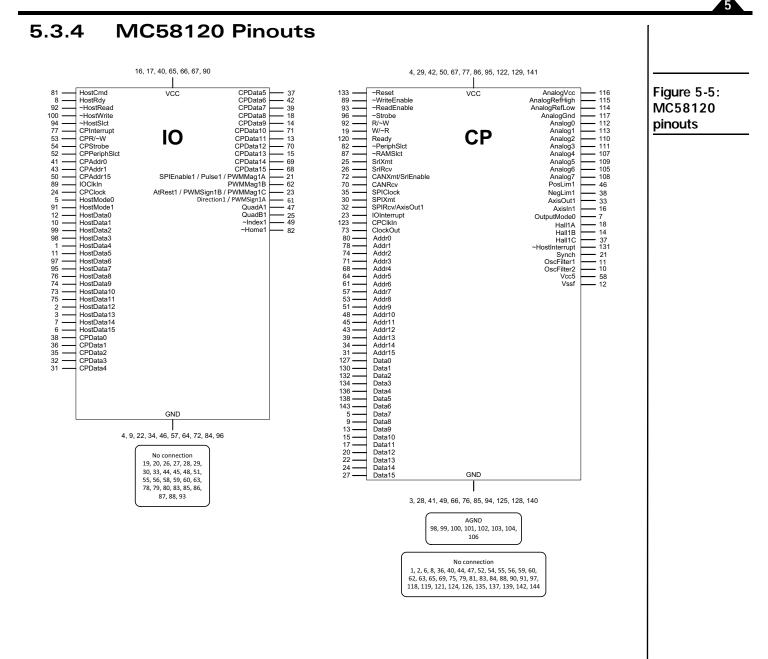

| 5-5        | MC58120 pinouts                                    |

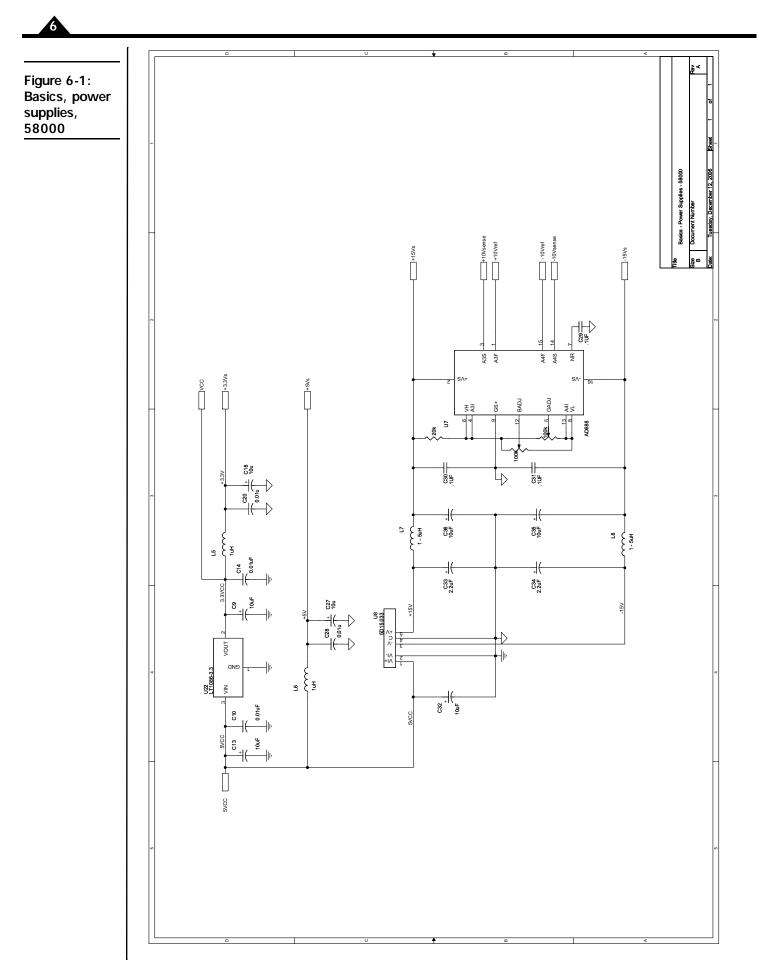

| 6-1        | Basics, power supplies, 58000                      |

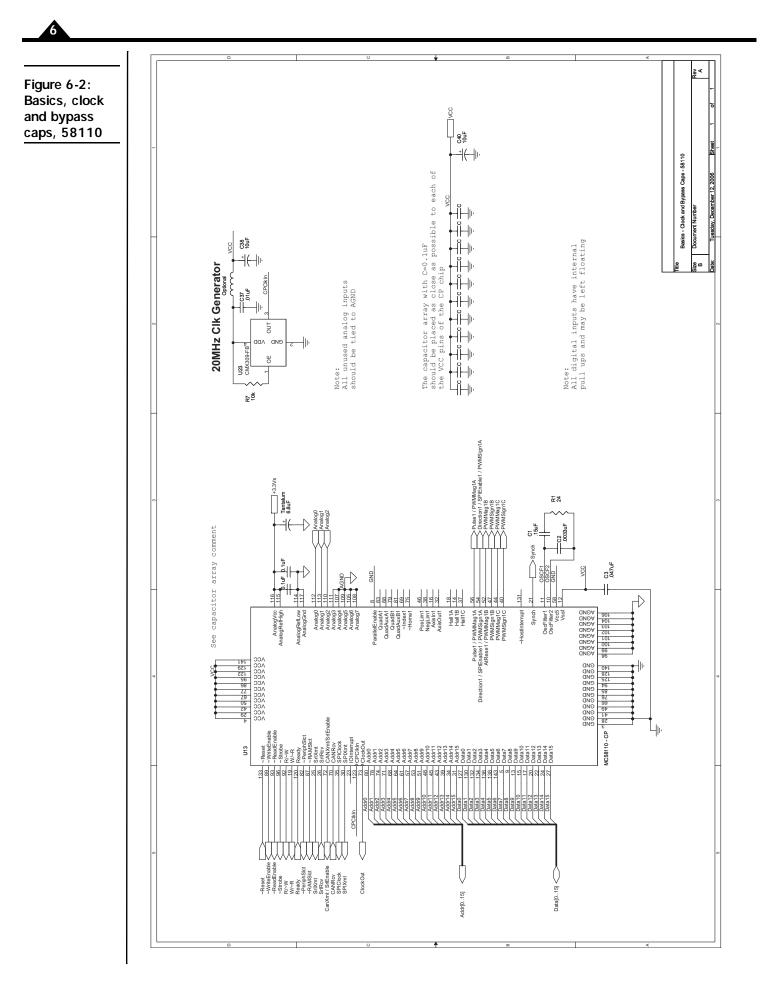

| 6-2        | Basics, clock and bypass caps, 5811068             |

| 6-3        | Basics, clock and bypass caps, 5842069             |

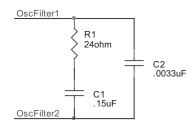

| 6-4        | Oscillator filter circuit                          |

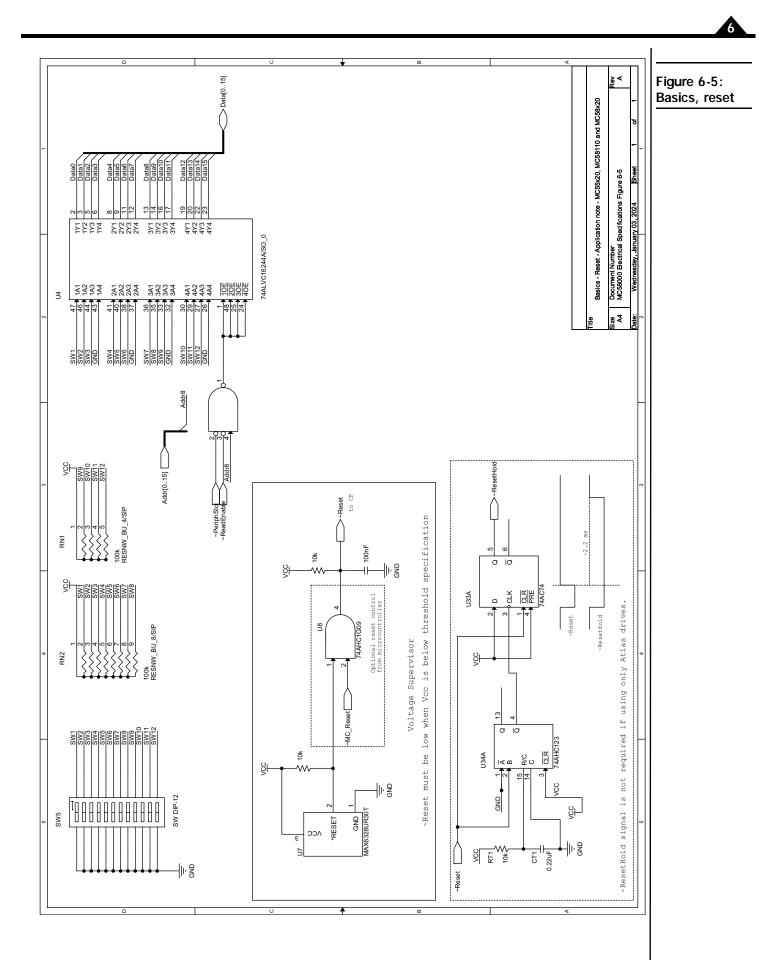

| 6-5        | Basics, reset                                      |

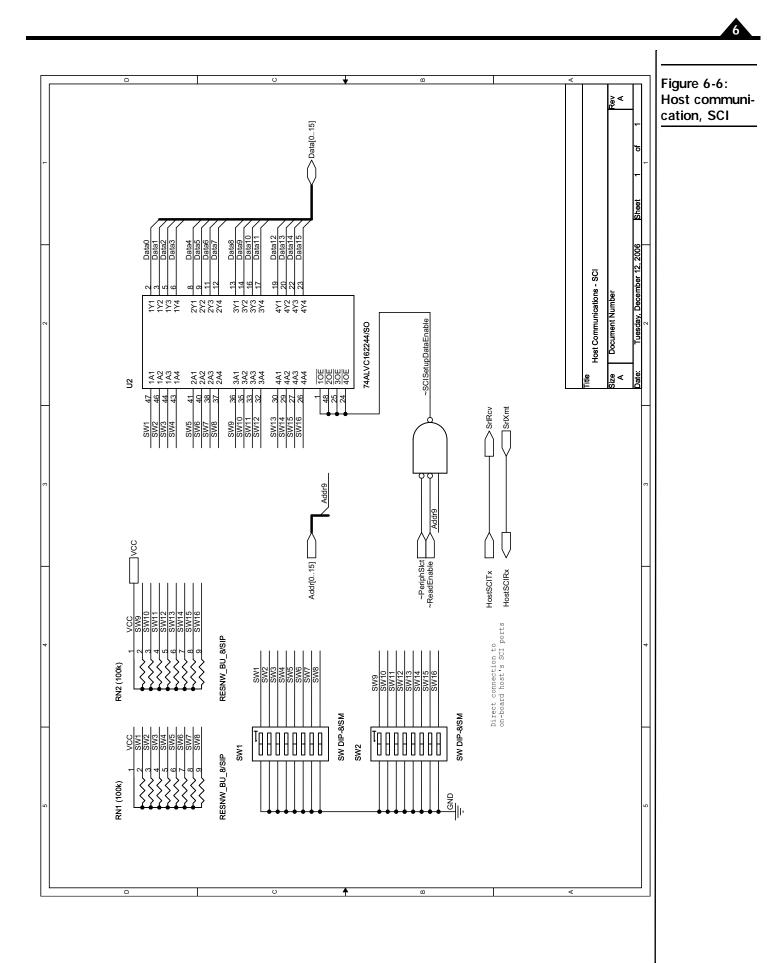

| 6-6        | Host communication, SCI73                          |

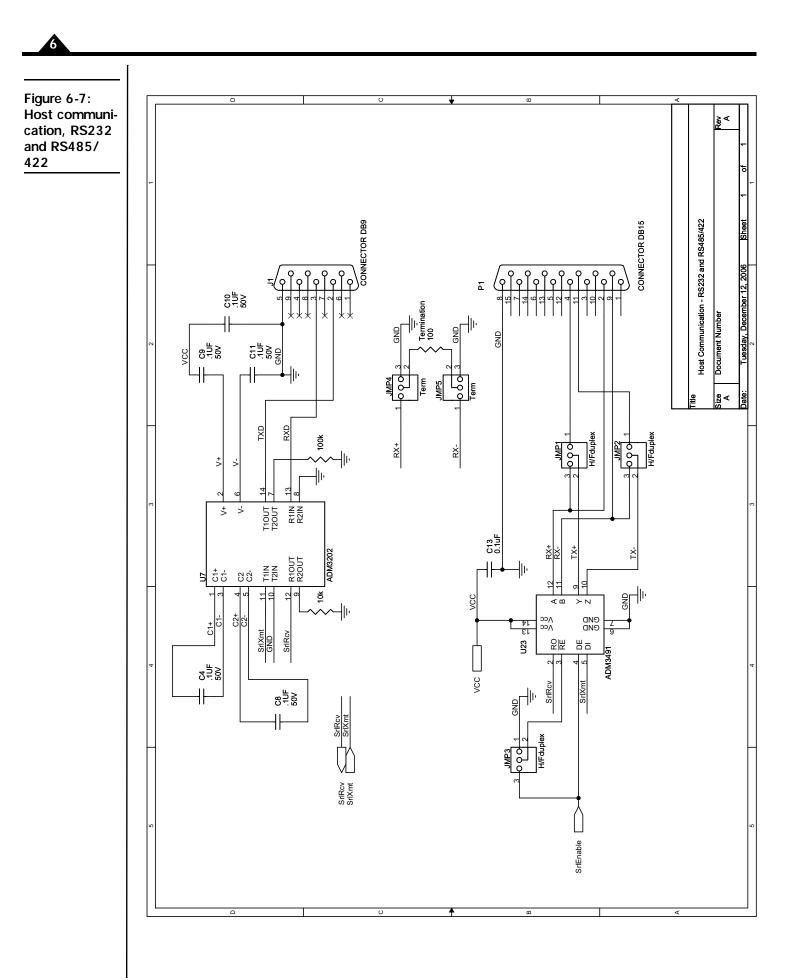

| 6-7        | Host communication, RS232 and RS485/42276          |

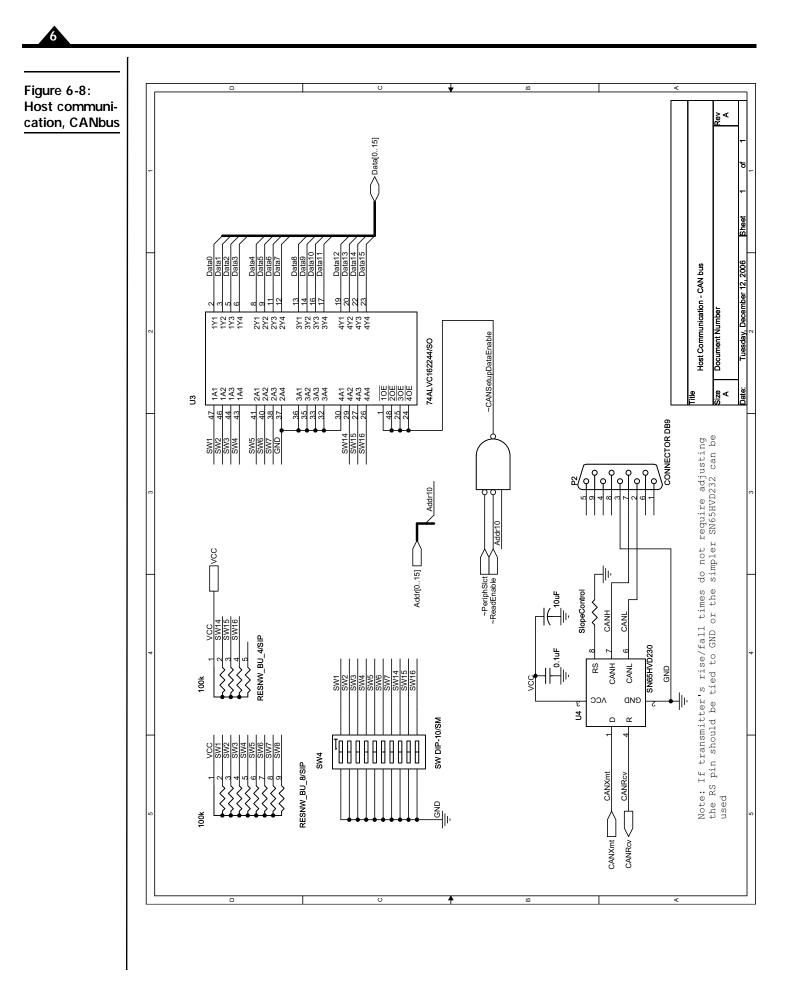

| 6-8        | Host communication, CANbus                         |

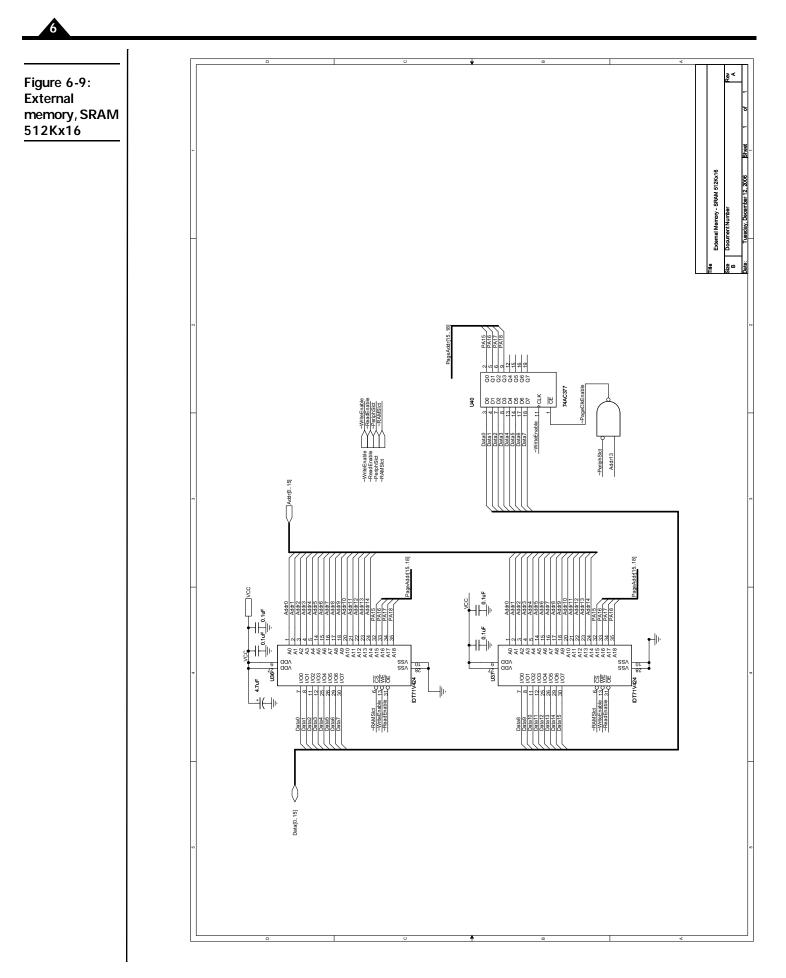

| 6-9        | External memory, SRAM 512Kx1680                    |

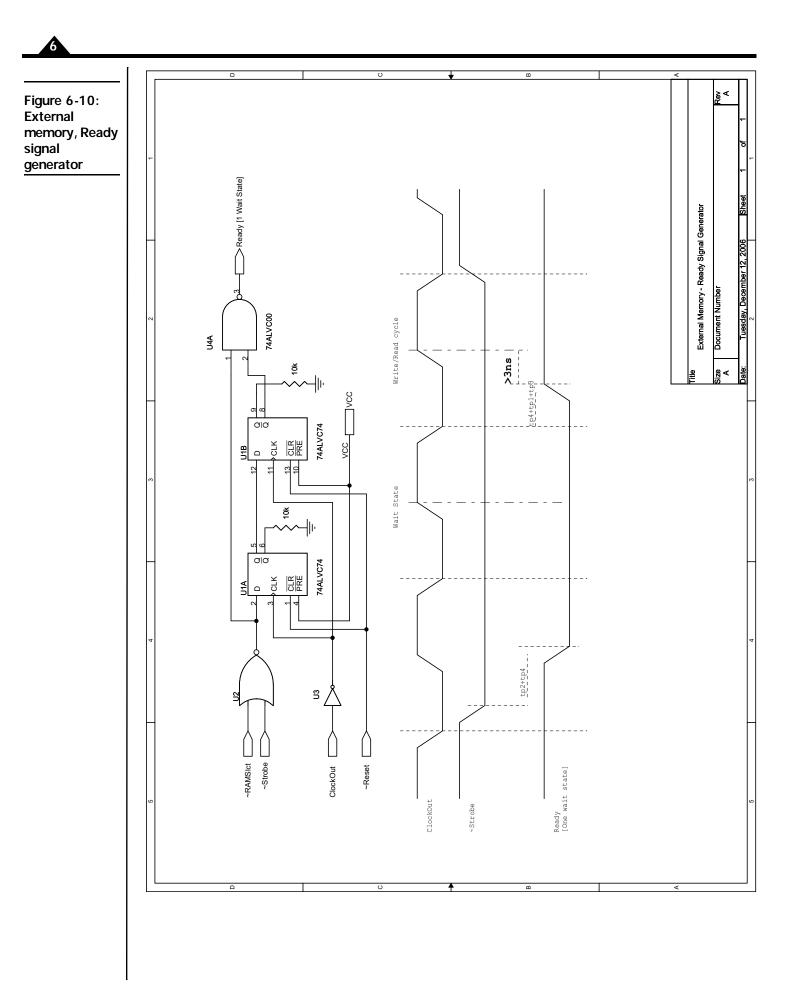

| 6-10       | External memory, Ready signal generator82          |

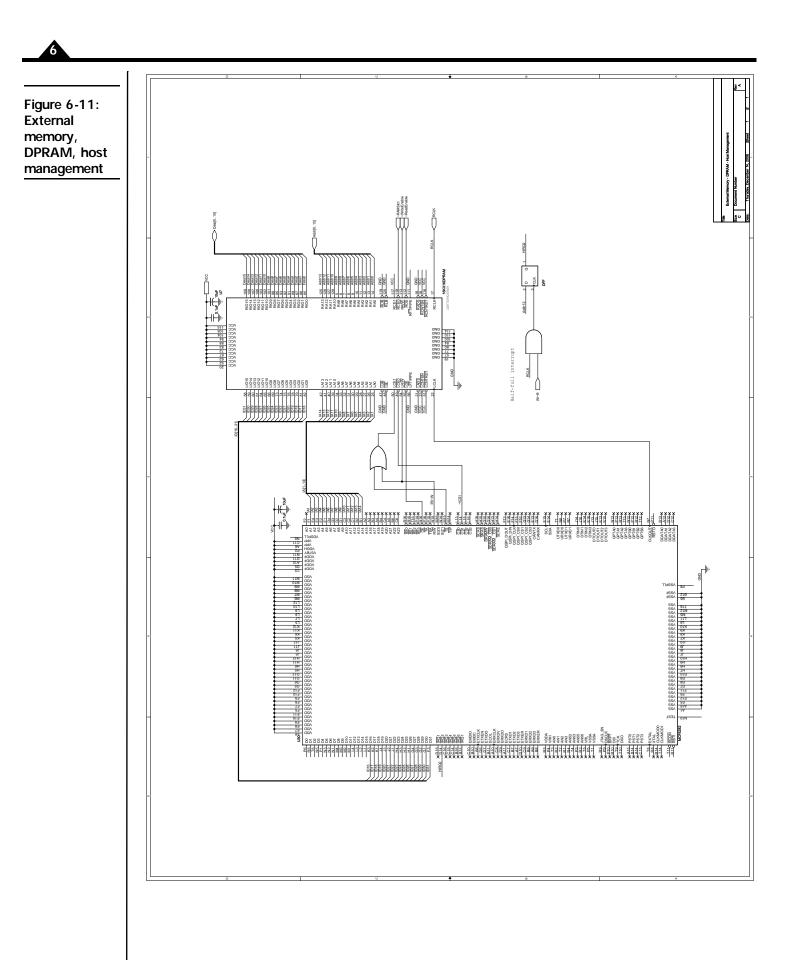

| 6-11       | External memory, DPRAM, host management84          |

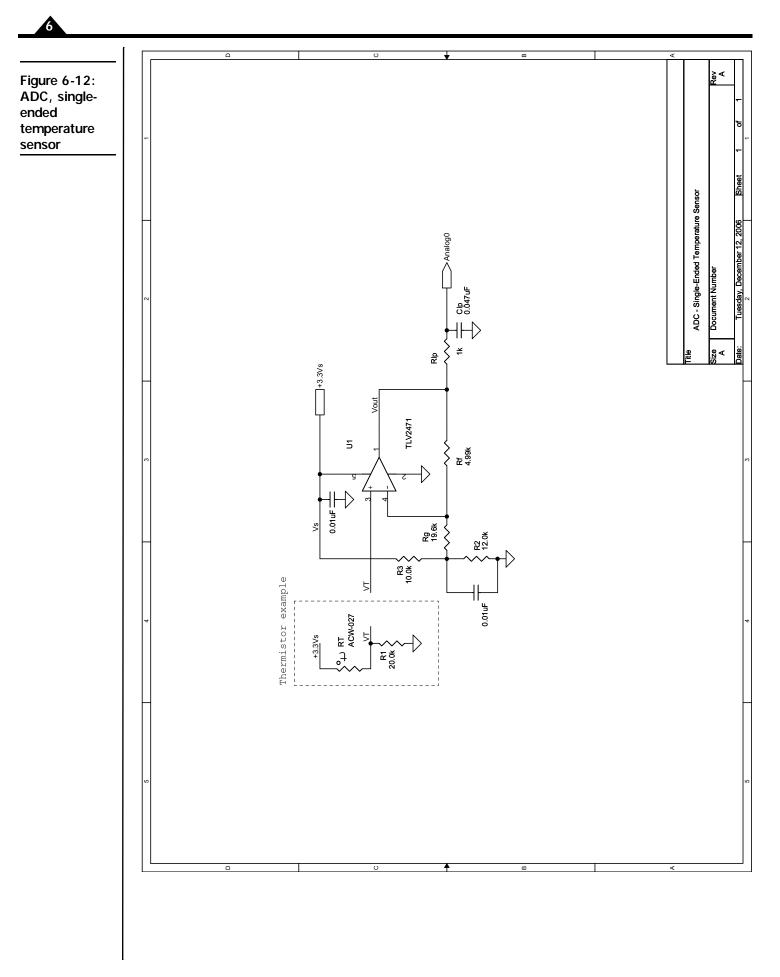

| 6-12       | ADC, single-ended temperature sensor               |

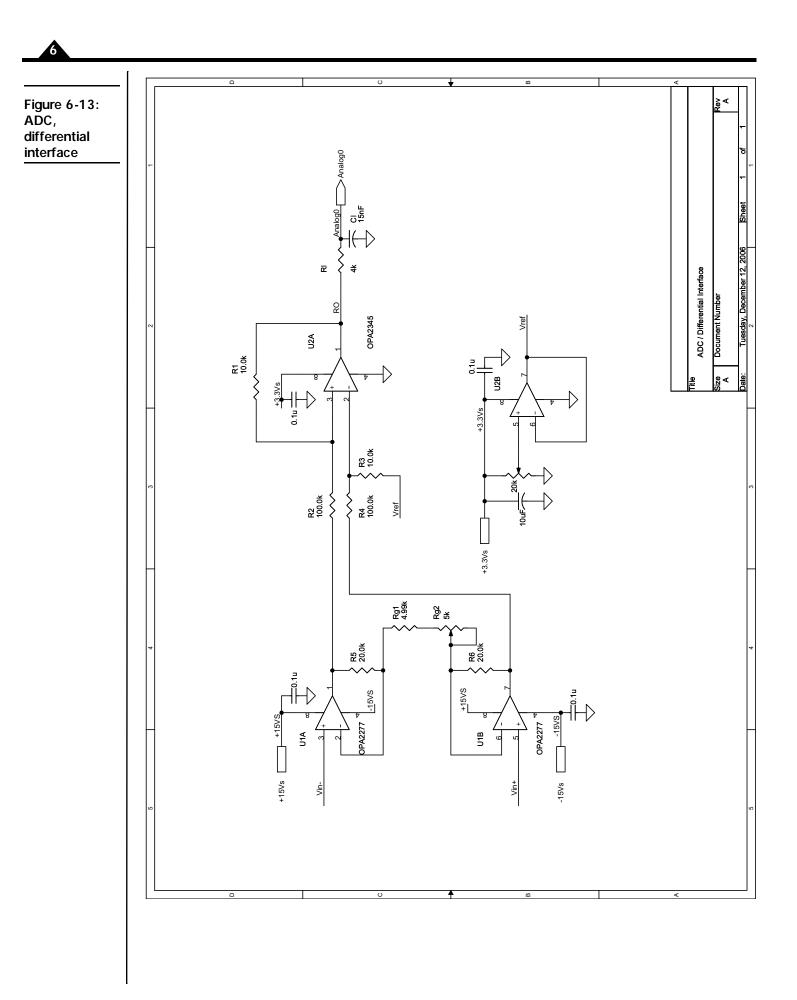

| 6-13       | ADC, differential interface                        |

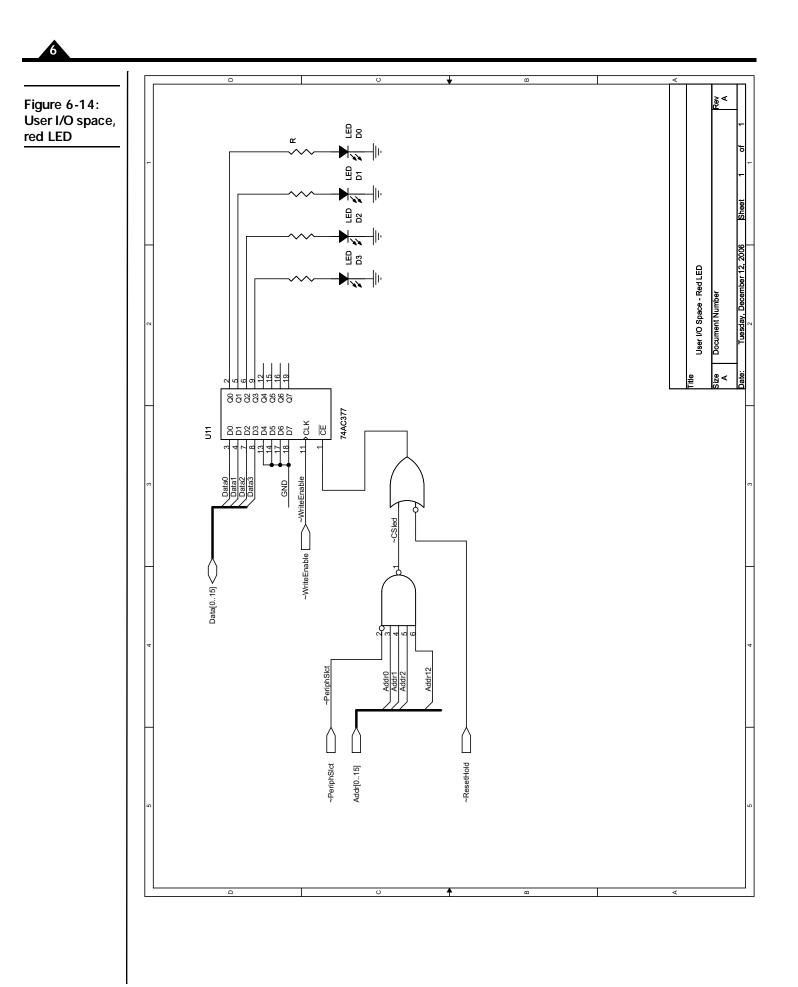

| 6-14       | User I/O space, red LED                            |

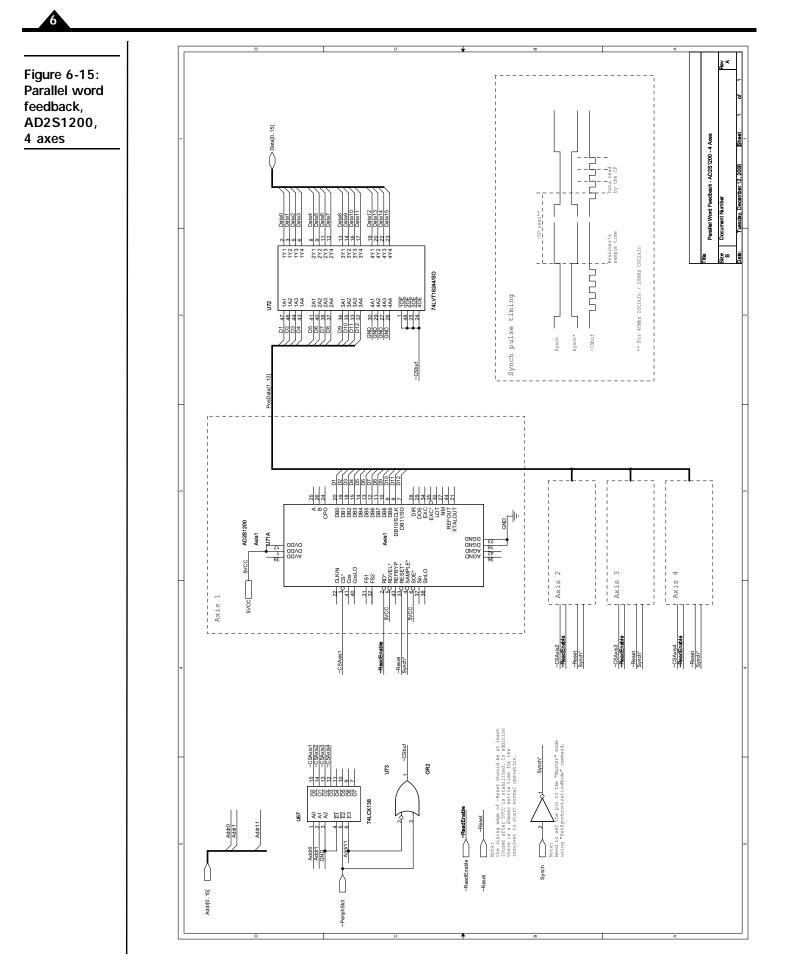

| 6-15       | Parallel word feedback, AD2S1200, 4 axes92         |

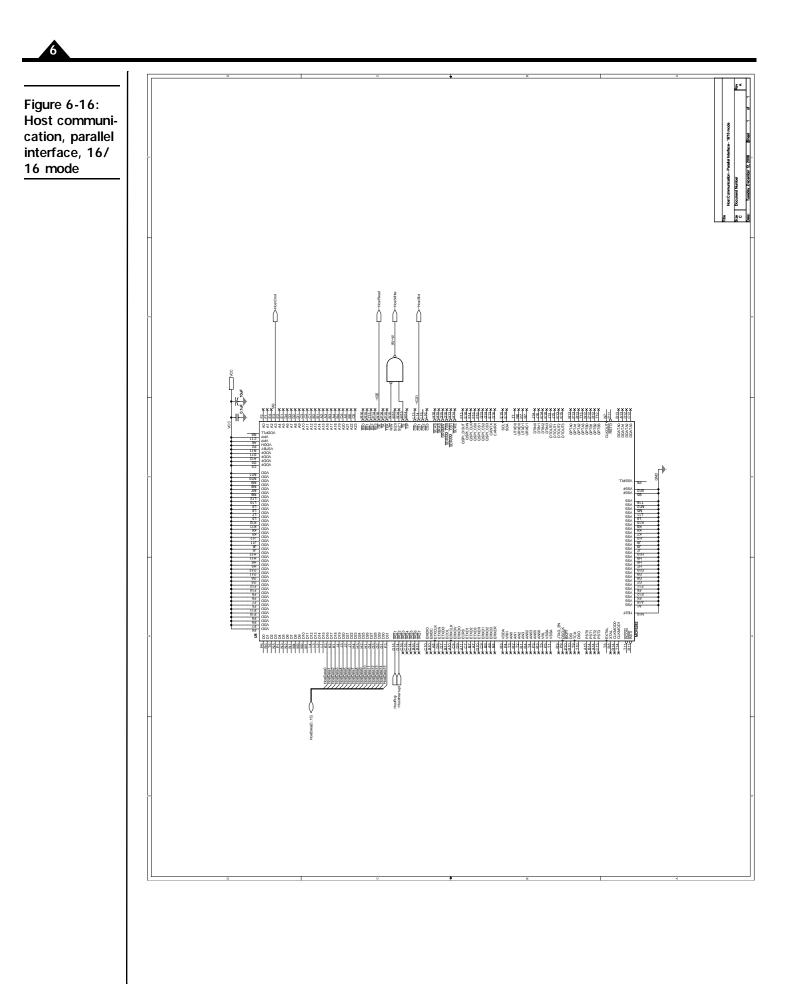

| 6-16       | Host communication, parallel interface, 16/16 mode |

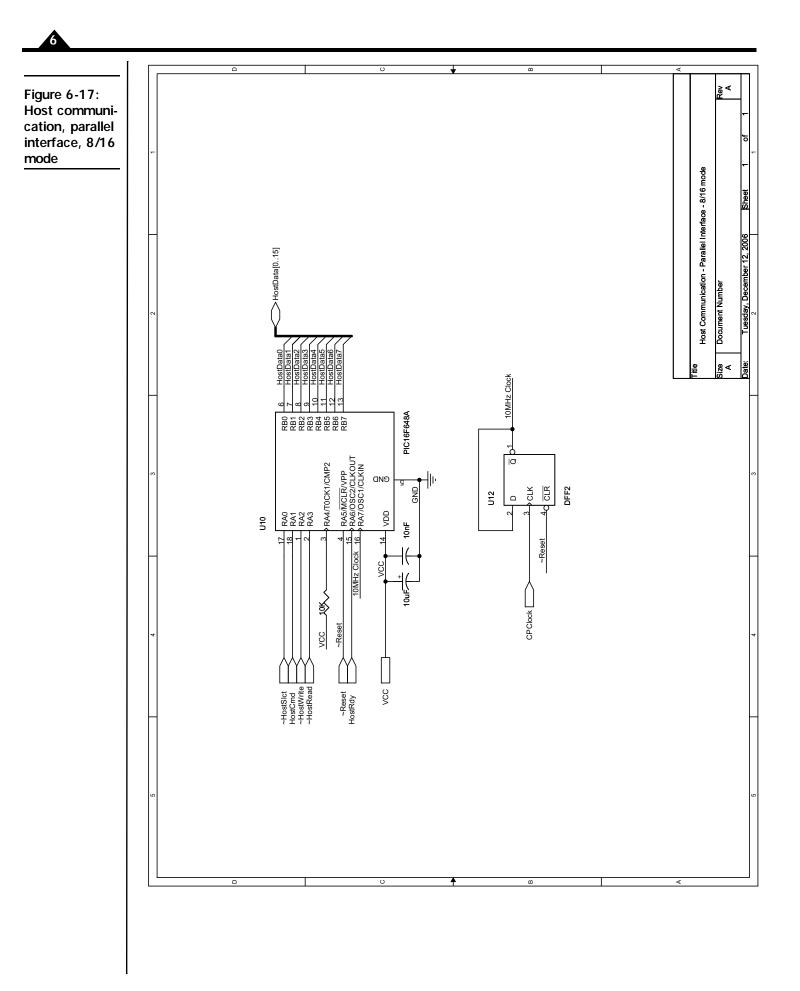

| 6-17       | Host communication, parallel interface, 8/16 mode  |

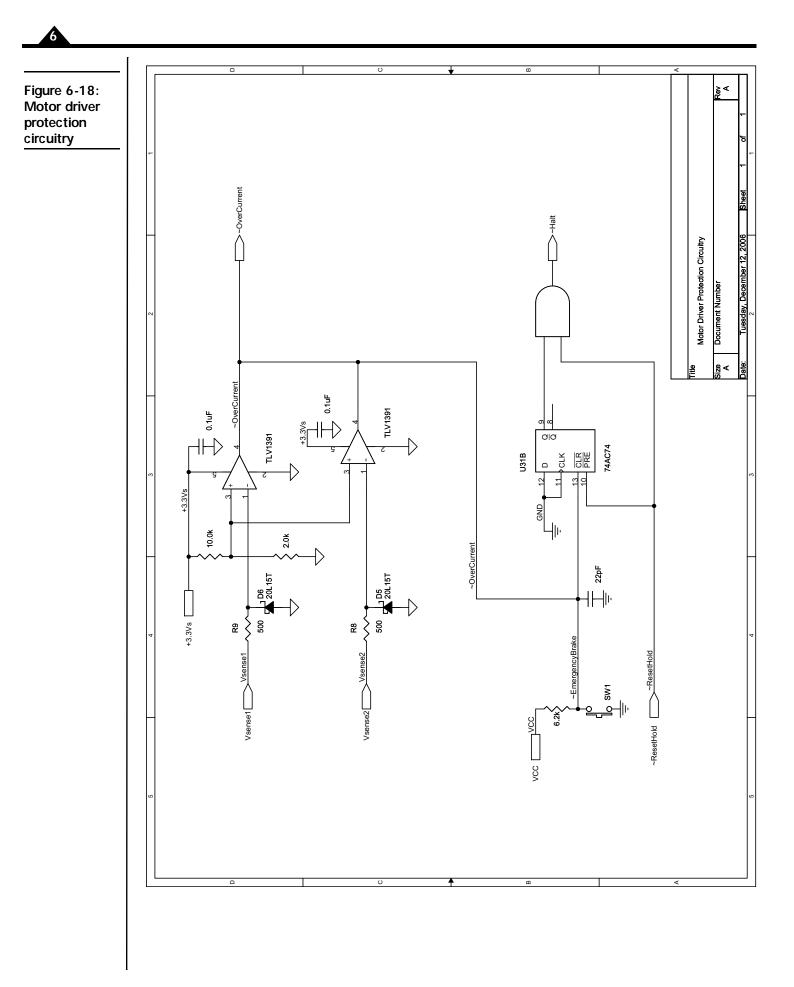

| 6-18       | Motor driver protection circuitry                  |

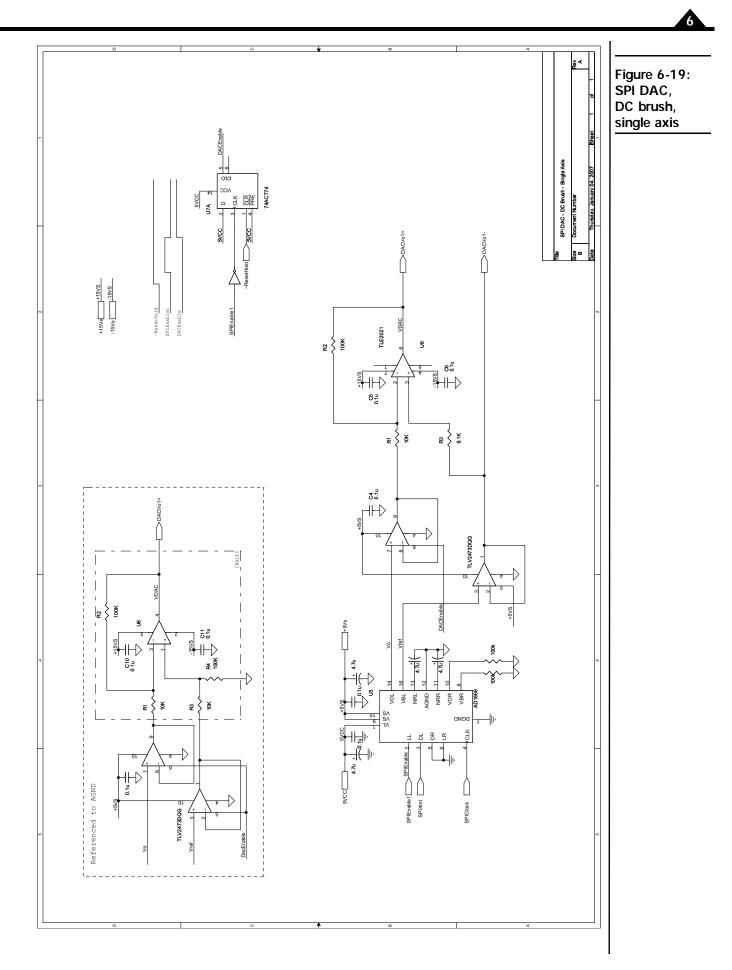

| 6-19       | SPI DAC, DC brush, single axis                     |

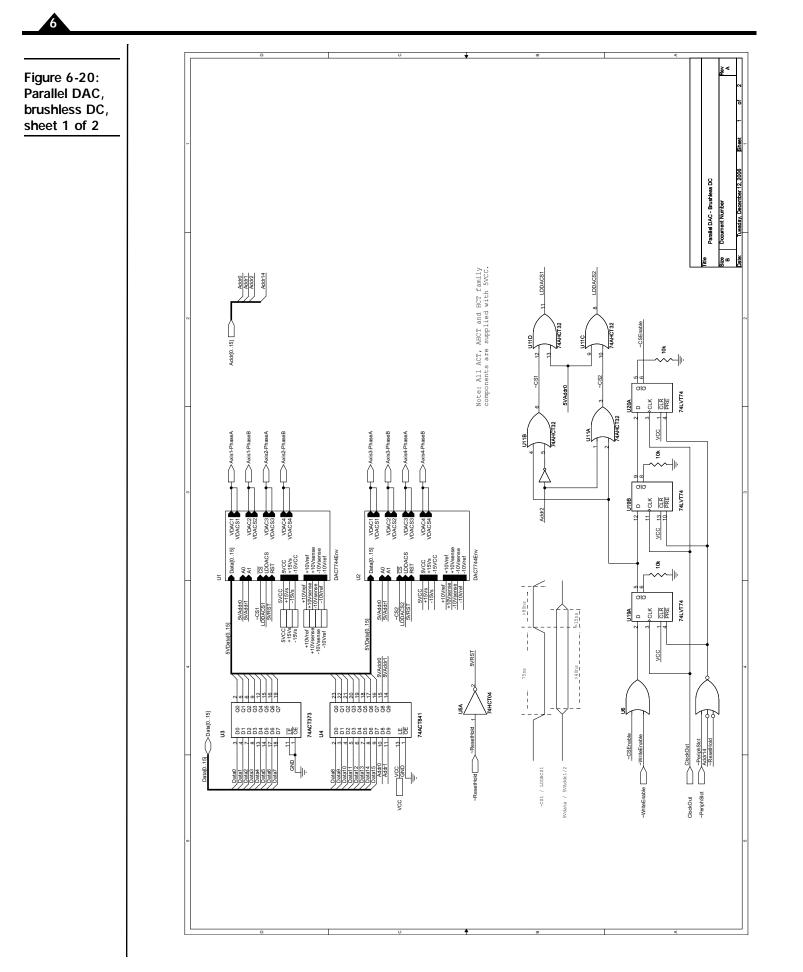

| 6-20       | Parallel DAC, brushless DC, sheet 1 of 2           |

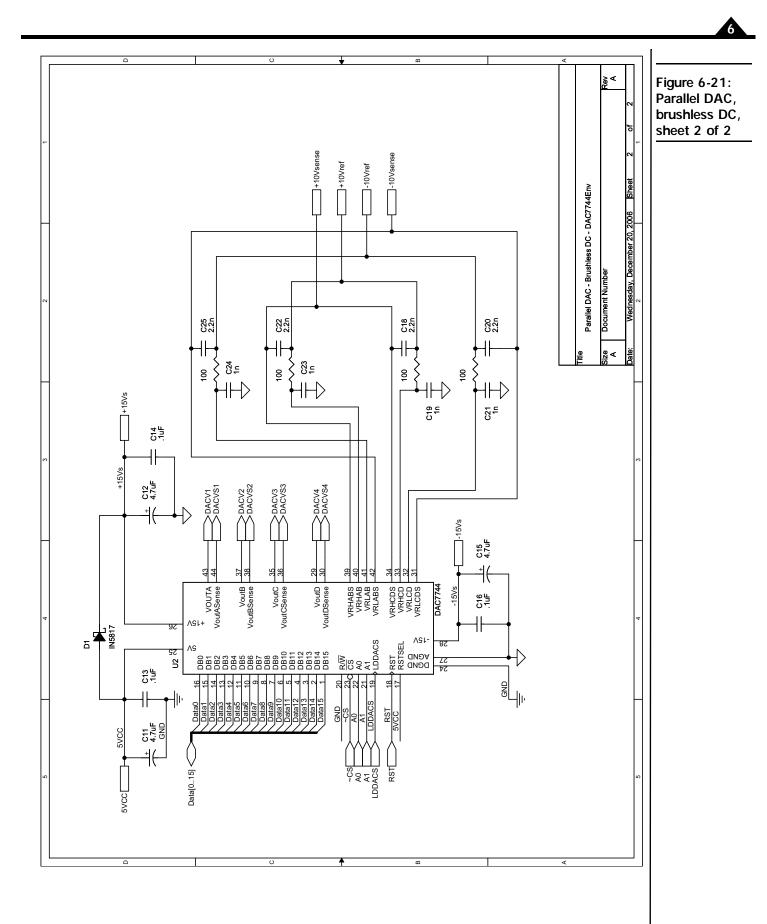

| 6-21       | Parallel DAC, brushless DC, sheet 2 of 2           |

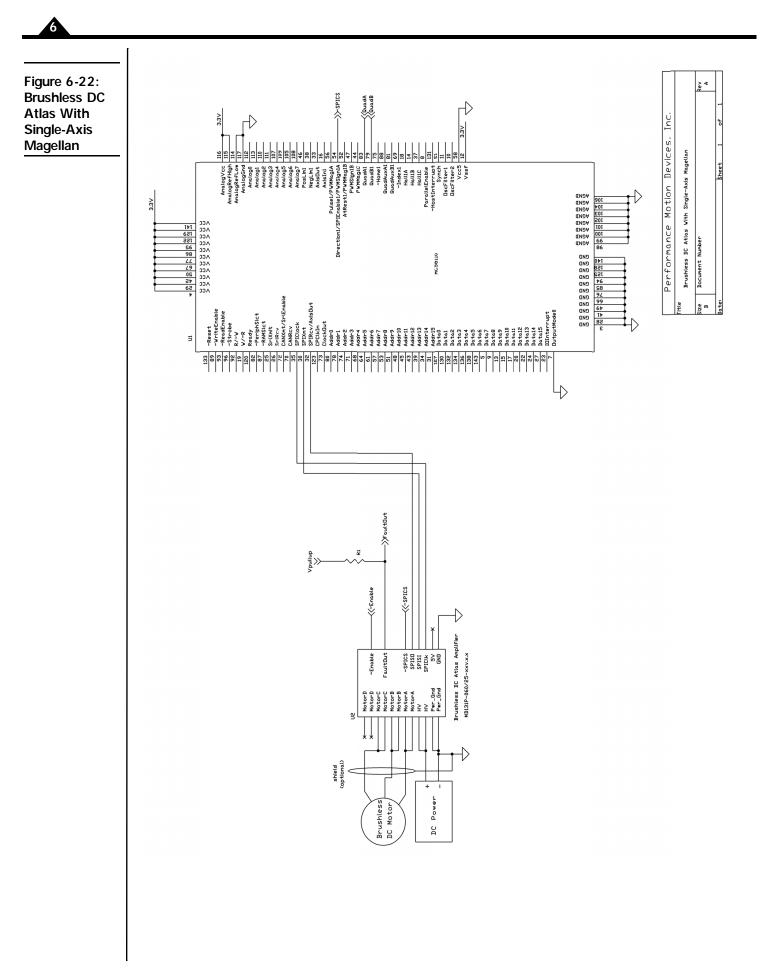

| 6-22       | Brushless DC Atlas With Single-Axis Magellan       |

|            |                                                    |

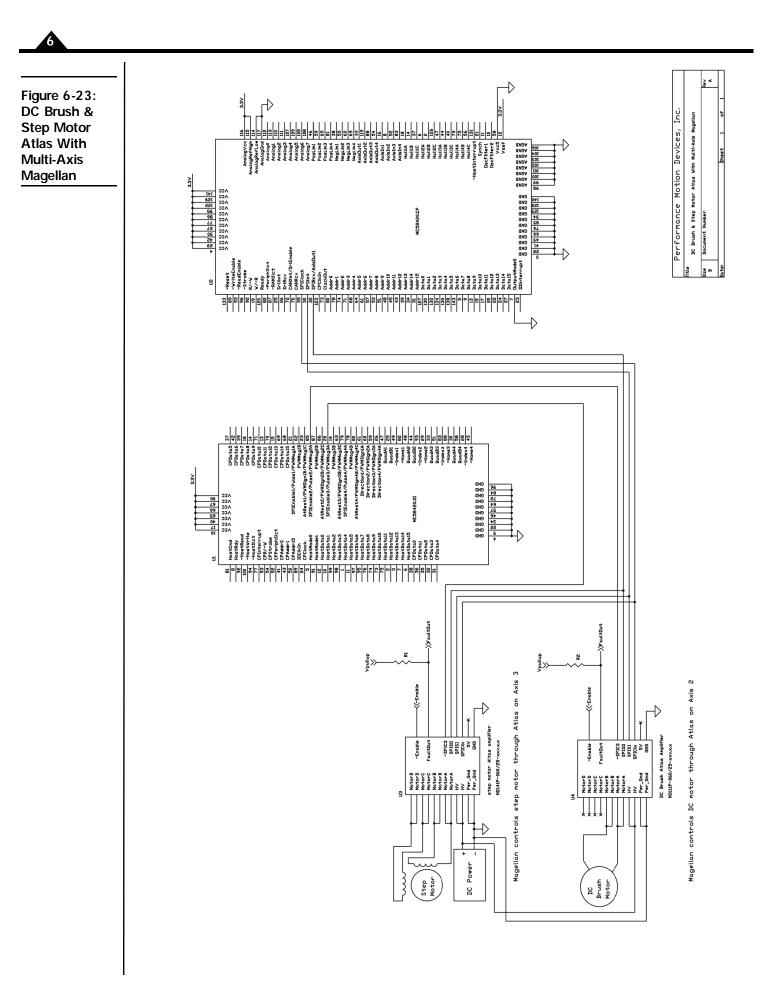

| 6-23 | DC Brush & Step Motor Atlas With Multi-Axis Magellan |     |

|------|------------------------------------------------------|-----|

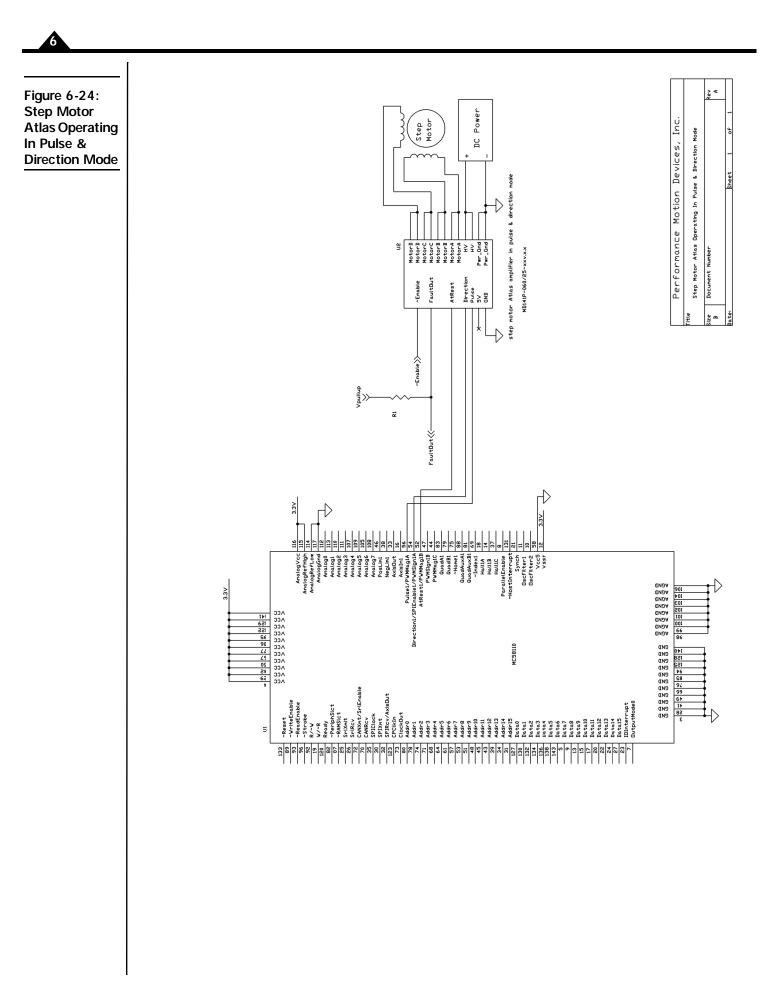

| 6-24 | Step Motor Atlas Operating In Pulse & Direction Mode |     |

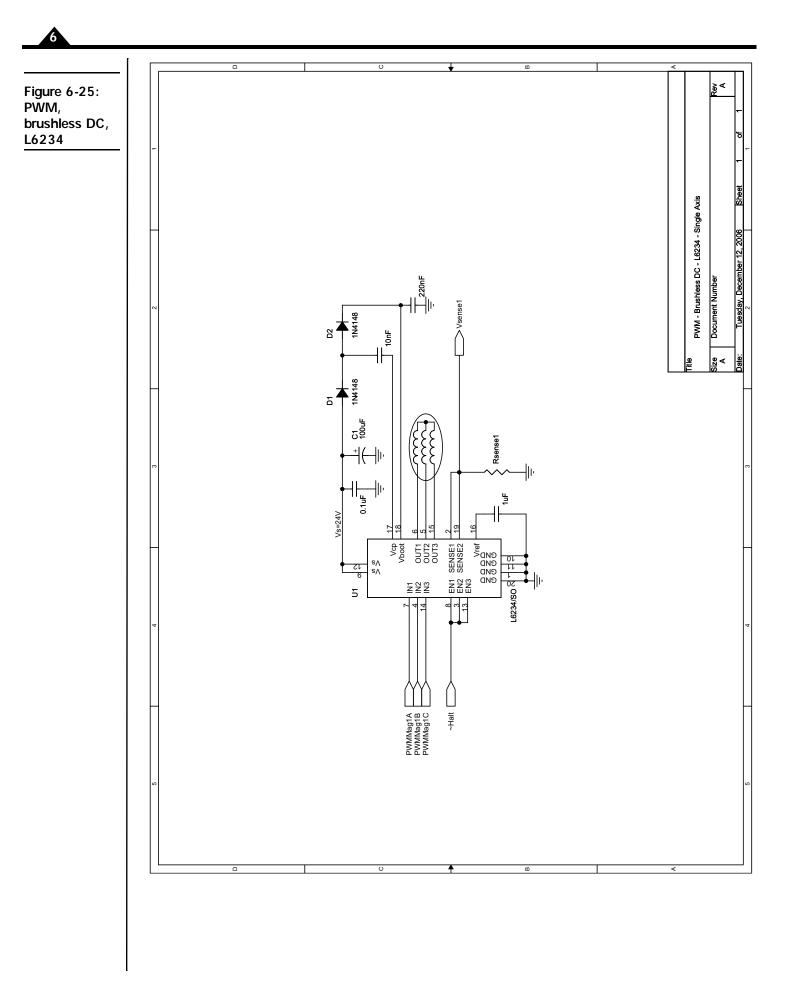

| 6-25 | PWM, brushless DC, L6234                             | 114 |

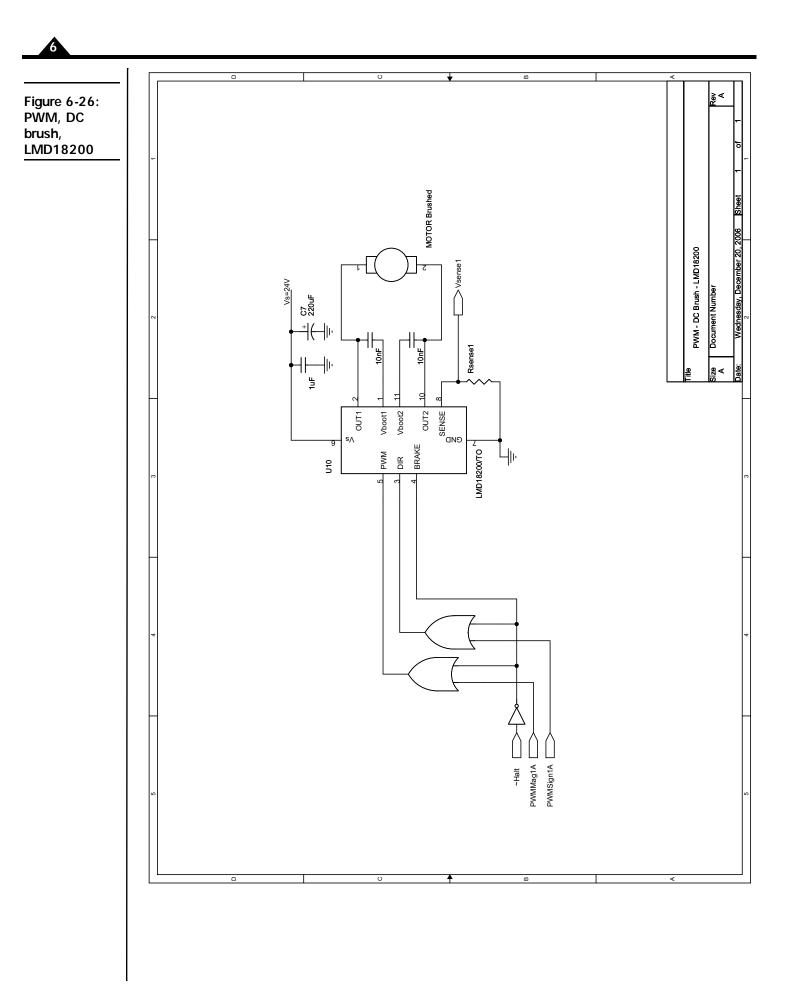

| 6-26 | PWM, DC brush, LMD18200                              |     |

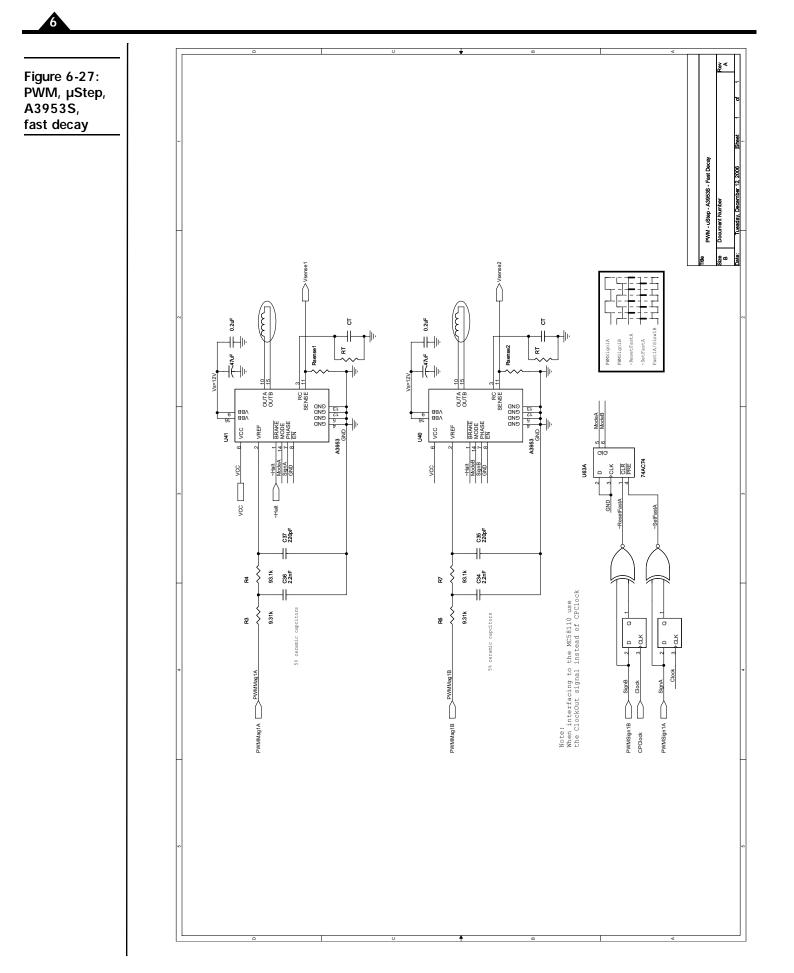

| 6-27 | PWM, μStep, A3953S, fast decay                       | 118 |

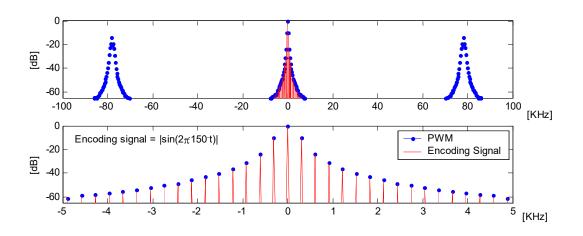

| 6-28 | Encoded PWM signal spectra                           |     |

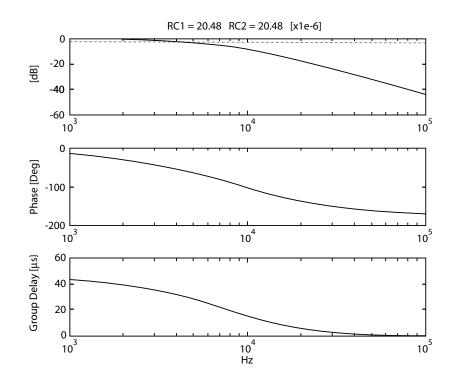

| 6-29 | Filter frequency response                            |     |

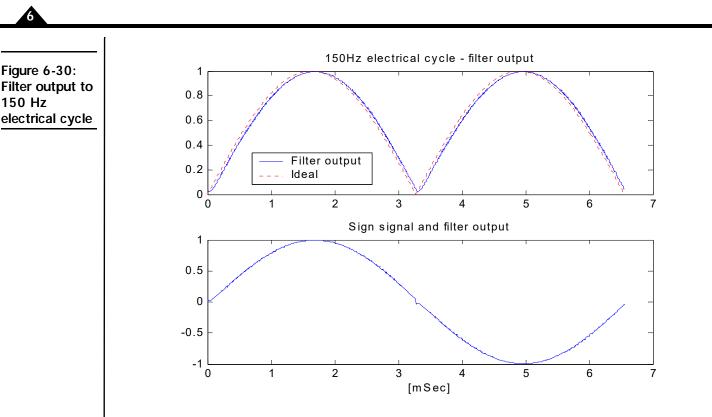

| 6-30 | Filter output to 150 Hz electrical cycle             |     |

| 6-31 | Pulse and direction, A3977                           |     |

# 1. The MC50000 Family

### In This Chapter

Magellan Motion Control IC Family Overview

MC58420-Series ICs & Developer Kit

### **Magellan Motion Control IC Family** 1.1 **Overview**

|                                   | MC58000 Series<br>(Except MC58113)                     | MC55000 Series    | MC58113 Series                              |

|-----------------------------------|--------------------------------------------------------|-------------------|---------------------------------------------|

| # of axes                         | 1, 2, 3, 4                                             | 1, 2, 3, 4        | I+ (primary & aux<br>channel encoder input) |

| Motor types supported             | DC Brush, Brushless DC,                                | Step motor        | DC Brush, Brushless DC,                     |

|                                   | step motor                                             | I                 | step motor                                  |

| Output format                     | SPI Atlas, PWM, DAC,                                   | Pulse & direction | SPI Atlas, PWM, DAC,                        |

|                                   | pulse & direction                                      |                   | pulse & direction                           |

| Parallel host communication       | · √                                                    | $\checkmark$      | 1                                           |

| Serial host communication         | $\checkmark$                                           | √                 | $\checkmark$                                |

| CAN 2.0B host communication       | $\checkmark$                                           | √                 | $\checkmark$                                |

| SPI host communication            |                                                        |                   | √                                           |

| Incremental encoder input         | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| Parallel word device input        | $\checkmark$                                           | $\checkmark$      |                                             |

| Index & Home signals              | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| Position capture                  | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| Directional limit switches        | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| PWM output                        | $\checkmark$                                           |                   | ✓                                           |

| Parallel DAC output               | $\checkmark$                                           |                   |                                             |

| SPI Atlas interface               | $\checkmark$                                           |                   | $\checkmark$                                |

| SPI DAC output                    | $\checkmark$                                           |                   | $\checkmark$                                |

| Pulse & direction output          | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| Digital current control           | <ul> <li>✓ (with Atlas)</li> </ul>                     |                   | $\checkmark$                                |

| Field oriented control            | <ul> <li>✓ (with Atlas)</li> </ul>                     |                   | $\checkmark$                                |

| Under/overvoltage sense           | <ul> <li>✓ (with Atlas)</li> </ul>                     |                   | $\checkmark$                                |

| I <sup>2</sup> T Current foldback | <ul><li>✓ (with Atlas)</li></ul>                       |                   | $\checkmark$                                |

| DC Bus shunt resistor control     |                                                        |                   | $\checkmark$                                |

| Overtemperature sense             | <ul> <li>✓ (with Atlas)</li> </ul>                     |                   | √                                           |

| Short circuit sense               | <ul> <li>✓ (with Atlas)</li> </ul>                     |                   | $\checkmark$                                |

| Trapezoidal profiling             | $\checkmark$                                           | √                 | √                                           |

| Velocity profiling                | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| S-curve profiling                 | $\checkmark$                                           | $\checkmark$      | √                                           |

| Electronic gearing                | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| On-the-fly changes                | $\checkmark$                                           | $\checkmark$      | $\checkmark$                                |

| PID position servo loop           | $\checkmark$                                           |                   | $\checkmark$                                |

| Dual biquad filters               | $\checkmark$                                           |                   | $\checkmark$                                |

| Dual encoder loop                 | <ul> <li>✓ (multi-axis configurations only)</li> </ul> |                   | $\checkmark$                                |

| Programmable derivative sampling  | configurations only)                                   |                   |                                             |

| time                              | $\checkmark$                                           |                   | $\checkmark$                                |

| Feedforward (accel & vel)         | $\checkmark$                                           |                   | $\checkmark$                                |

|                             | MC58000 Series          | MC55000 Series                       | MC58113 Series          |

|-----------------------------|-------------------------|--------------------------------------|-------------------------|

|                             | (Except MC58113)        |                                      |                         |

| Data trace/diagnostics      | $\checkmark$            | $\checkmark$                         | $\checkmark$            |

| Motion error detection      | $\checkmark$            | <ul> <li>✓ (with encoder)</li> </ul> | $\checkmark$            |

| Axis settled indicator      | $\checkmark$            | <ul> <li>✓ (with encoder)</li> </ul> | $\checkmark$            |

| Analog input                | $\checkmark$            | $\checkmark$                         | $\checkmark$            |

| Programmable bit output     | $\checkmark$            | $\checkmark$                         | $\checkmark$            |

| Software-invertible signals | $\checkmark$            | $\checkmark$                         | $\checkmark$            |

| User-defined I/O            | $\checkmark$            | $\checkmark$                         |                         |

| Internal Trace Buffer       |                         |                                      | $\checkmark$            |

| External RAM support        | $\checkmark$            | $\checkmark$                         |                         |

| Multi-chip synchronization  | $\checkmark$            |                                      | $\checkmark$            |

| Chipset configurations      | MC58420 (4 axes, 2 ICs) | MC55420 (4 axes, 2 ICs)              | MC51113 (1+ axis, 1 IC) |

|                             | MC58320 (3 axes, 2 ICs) | MC55320 (3 axes, 2 ICs)              | MC53113 (1+ axis, 1 IC) |

|                             | MC58220 (2 axes, 2 ICs) | MC55220 (2 axes, 2 ICs)              | MC54113 (1+ axis, 1 IC) |

|                             | MC58120 (1 axis, 2 ICs) | MC55120 (1 axis, 2 ICs)              | MC58113 (1+ axis, 1 IC) |

|                             | MC58110 (1 axis, 1 IC)  | MC55110 (1 axis, 1 IC)               |                         |

| IC Package: CP chip         | MC58x20: 144 pin TQFP   | MC55x20: 144 pin TQFP                | 100 pin TQFP            |

| -                           | MC58110: 144 pin TQFP   | MC55110: 144 pin TQFP                |                         |

| IC Package: IO chip         | MC58x20: 100 pin TQFP   | MC55x20: 100 pin TQFP                | N/A                     |

|                             | MC58110: NA             | MC55110: NA                          |                         |

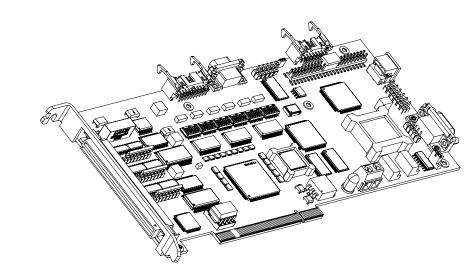

## 1.2 MC58420-Series ICs & Developer Kit

There are five members of the MC58420-series ICs; MC58420, MC58320, MC58220, MC58120, and MC58110. A single developer kit supports all of these ICs:

| Developer Kit p/n | Installed IC | Motors Supported                   |

|-------------------|--------------|------------------------------------|

| DK58420           | MC58420      | DC Brush, Brushless DC, step motor |

The DK58420 developer kit comes installed with the four axis MC58420CP chip. For users interested in other MC58000 chips, for example MC58320, MC58220, MC58120, or MC58110 (three, two, one, and one axes respectively) there are two options. The first is to separately order the desired MC58000 family CP and take advantage of the fact that the CP chip is socketed by swapping the desired IC with the MC58420CP.

Figure 1-1: DK58420 Board

MC58000 Electrical Specifications

The second option is to leave the MC58420 installed and disable one or more higher order axes and reduce the sample time to match the default sample time of the desired IC. For example to make the installed four axis MC58420 mimic a two axis MC58220 the **SetOperatingMode** command would be used to disable axes #3 and #4, and the **SetSampleTime** command would be used to set the sample time to 153.6  $\mu$ Sec.

Note that the Magellan IO chip that accompanies the CP chip supports one, two, three, and four axes CP chips so there is no need to swap or change the functionality of the Magellan IO chip installed in the developer kit.

Note that throughout this manual the term MC58000 means the complete product family; MC58420, MC58320, MC58220, MC58120, and MC58110.

This page intentionally left blank.

# **2. Functional Characteristics**

5

### In This Chapter

- Configurations, Parameters, and Performance

- Physical Characteristics and Mounting Dimensions

- Absolute Maximum Environmental and Electrical Ratings

- MC58110 System Configuration Single Chip, 1 Axis Control

- MC58x20 System Configuration Two Chip, 1 To 4 Axis Control

## 2.1 Configurations, Parameters, and Performance

| Configuration                    | 4 axes (MC58420)                                                                              |

|----------------------------------|-----------------------------------------------------------------------------------------------|

| C                                | 3 axes (MC58320)                                                                              |

|                                  | 2 axes (MC58220)                                                                              |

|                                  | I axis (MC58120 or MC58110)                                                                   |

| Operating modes                  | Servo                                                                                         |

|                                  | Closed loop (motor command is driven from output of servo filter)                             |

|                                  | Open loop (motor command is driven from user-programmed register)                             |

|                                  | Microstepping                                                                                 |

|                                  | Open loop (motor command is driven from output of trajectory generator & microstep            |

|                                  | generator; encoder input used for stall detection)                                            |

|                                  | Pulse & Direction                                                                             |

|                                  | Open loop (pulse generator is driven by trajectory generator output, encoder input used       |

|                                  | for stall detection)                                                                          |

| Communication modes              | 8/16 parallel 8-bit external parallel bus with 16-bit command word size                       |

|                                  | 16/16 parallel16-bit external parallel bus with 16-bit command word size                      |

|                                  | Point to point asynchronous serial                                                            |

|                                  | Multi-drop asynchronous serial                                                                |

|                                  | CAN bus 2.0B, protocol co-exists with CANOpen, 11-bit identifier.                             |

| Serial port baud rate range      | 1,200 baud to 460,800 baud                                                                    |

| CAN port transmission rate range | 10,000 baud to 1,000,000 baud                                                                 |

| Profile modes                    | S-curve point-to-point Position, velocity, acceleration, deceleration, and jerk<br>parameters |

|                                  | Trapezoidal point-to-point Position, velocity, acceleration, and deceleration                 |

|                                  | parameters                                                                                    |

|                                  | Velocity-contouring Velocity, acceleration, and deceleration parameters                       |

|                                  | Electronic Gear Encoder or trajectory position of one axis used to drive                      |

|                                  | a second axis. Master and slave axes and gear ratio                                           |

|                                  | parameters.                                                                                   |

| Position range                   | -2,147,483,648 to +2,147,483,647 counts or steps                                              |

| Velocity range                   | -32,768 to +32,767 counts or steps per cycle                                                  |

| _                                | with a resolution of 1/65,536 counts or steps per cycle                                       |

| Acceleration and deceleration ranges       | 0 to +32,767 counts or steps per cycle <sup>2</sup><br>with a resolution of 1/65,536 counts or steps per cycle <sup>2</sup>                                                                       |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jerk range                                 | 0 to $\frac{1}{2}$ counts or steps per cycle <sup>3</sup> with a resolution of 1/4,294,967,296 counts or steps per cycle <sup>3</sup>                                                             |

| Electronic gear ratio range                | -32,768 to +32,767 with a resolution of 1/65,536 (negative and positive direction)                                                                                                                |

| Filter modes                               | Scalable PID + Velocity feedforward + Acceleration feedforward + Bias. Also includes integration limit, settable derivative sampling time, output motor command limiting and two bi-quad filters. |

|                                            | Dual encoder feedback mode where auxiliary encoder is used for backlash compensation<br>16 bits                                                                                                   |

| Filter parameter resolution Position error | 32 bits                                                                                                                                                                                           |

| Position error tracking                    | Motion error windowAllows axis to be stopped upon exceeding programmable                                                                                                                          |

| Position error tracking                    | window                                                                                                                                                                                            |

|                                            | Tracking windowAllows flag to be set if axis exceeds a programmable position window                                                                                                               |

|                                            | Axis settledAllows flag to be set if axis exceeds a programmable<br>position window for a programmable amount of time                                                                             |

|                                            | after trajectory motion is complete                                                                                                                                                               |

| Motor output modes                         | PWM10-bit resolution at 20 kHz, or                                                                                                                                                                |

| ·                                          | 8-bit resolution at 80 kHz                                                                                                                                                                        |

|                                            | Parallel DAC-compatible 16 bits                                                                                                                                                                   |

|                                            | SPI DAC-compatible 16 bits                                                                                                                                                                        |

|                                            | Pulse and directionMC58x20: 4.98 Mpulses/sec maximum<br>MC58110: 97.6 kpulses/sec maximum                                                                                                         |

|                                            | SPI AtlasFour-signal SPI interface with 16-bit packet commands                                                                                                                                    |

|                                            | and SPI Atlas protocol.                                                                                                                                                                           |

| Commutation rate                           | I0 kHz                                                                                                                                                                                            |

| Microstepping waveform                     | Sinusoidal                                                                                                                                                                                        |

| Microsteps per full step                   | Programmable, I to 256                                                                                                                                                                            |

| Maximum encoder rate                       | Incremental (up to 8 Mcounts/sec)                                                                                                                                                                 |

|                                            | Parallel-word (up to 160 Mcounts/sec)                                                                                                                                                             |

| Parallel encoder word size                 | 16 bits                                                                                                                                                                                           |

| Parallel encoder read rate                 | 20 kHz (reads all axes every 50 μsec)                                                                                                                                                             |

| Hall sensor inputs                         | 3 Hall effect inputs per axis (TTL level signals)                                                                                                                                                 |

| Cycle timing range                         | 51.2 microseconds to 1.048576 seconds                                                                                                                                                             |

| Minimum cycle time                         | 51.2 microseconds                                                                                                                                                                                 |

| Multi-chip synchronization                 | <i and="" between="" cycle<="" difference="" master="" servo="" slave="" th="" µsec=""></i>                                                                                                       |

| Limit switches                             | 2 per axis: one for each direction of travel                                                                                                                                                      |

| Position-capture triggers                  | 2 per axis: index and home signals                                                                                                                                                                |

| Other digital signals (per axis)           | l AxisIn signal per axis, l AxisOut signal per axis.                                                                                                                                              |

| Software-invertible signals                | Encoder A, Encoder B, Index, Home, AxisIn, AxisOut, PositiveLimit, NegativeLimit, HallA,<br>HallB, HallC (all individually programmable per axis), Pulse, Direction.                              |

| Analog input                               | 8 10-bit analog inputs                                                                                                                                                                            |

| User defined discrete I/O                  | 256 16-bit width user defined I/O                                                                                                                                                                 |

| RAM/external memory support                | 65,536 blocks of 32,768 16-bit words per block. Total accessible memory is 2,147,483,648 16-bit words.                                                                                            |

| Trace modes                                | one-time, continuous                                                                                                                                                                              |

| Maximum number of trace variables          | 4                                                                                                                                                                                                 |

| Number of traceable variables              | 31                                                                                                                                                                                                |

|                                            |                                                                                                                                                                                                   |

## 2.3 Absolute Maximum Environmental and Electrical Ratings

### 2.3.1 CP 58110, 58x20

| -0.3V to +4.6V |

|----------------|

| -0.3V to +5.5V |

| -0.3V to +4.6V |

| 32°C/W         |

| -40°C to 150°C |

| -65°C to 150°C |

| 20.0 MHz       |

|                |

### 2.3.2 IO 58x20

| Supply Voltage (Vcc)                    | -0.5V to +3.6V     |

|-----------------------------------------|--------------------|

| Input voltage (Vi)                      | -0.5V to Vcc +0.5V |

| Package thermal impedance ( $	heta$ JA) | 39.7°C/W           |

| Junction temperature range (Tj)         | -40°C to 150°C     |

| Storage Temperature (Ts)                | -65°C to 150°C     |

| Nominal Clock Frequency (Fclk)          | 40.0 MHz           |

## 2.4 MC58110 System Configuration – Single Chip, 1 Axis Control

The following figure shows the principal control and data paths in an MC58110 system.

The CP chip is a self-contained motion control IC. In addition to handling all system functions, the CP chip contains the profile generator, which calculates position, velocity, acceleration, and values for a trajectory. When an axis is configured for servo motor control, a digital servo filter controls the motor output signal. When an axis is configured for microstepping motor control, a commutator controls the motor output signal. In either case, one of four types of output can be generated:

- a Pulse-Width Modulated (PWM) signal output

- a DAC-compatible value routed via the data bus to the appropriate D/A converter

- a DAC-compatible value routed via the SPI port to the appropriate D/A converter

- an SPI Atlas bus-compatible bi-directional amplifier interface

If an axis is configured for step motor control, the CP chip generates pulse and direction signals. Axis position information returns to the motion control IC in the form of encoder feedback using either the incremental encoder input signals, or via the bus as parallel word input.

The MC58110 can co-exist in a CANOpen network as a slave device. It is CAN 2.0B compliant.

The shaded area shows the PLD/FPGA that must be provided by the designer if parallel communication is required. For a description and an example of the necessary logic (in schematic format) contact PMD.

### 2.5 MC58x20 System Configuration – Two Chip, 1 to 4 Axis Control

The following figure shows the principal control and data paths in an MC58x20 system.

The IO chip contains the parallel host interface, the incremental encoder input along with motor output signals that are configured as PWM or pulse and direction signals according to the motor type selected for each axis.

The CP chip contains the profile generator, which calculates position, velocity, acceleration, and values for a trajectory. When an axis is configured for servo motor control, a digital servo filter controls the motor output signal. When an axis is configured for microstepping motor control, a commutator controls the motor output signal. In either case, one of four types of output can be generated:

- a Pulse-Width Modulated (PWM) signal output

- a DAC-compatible value routed via the data bus to the appropriate D/A converter

- a DAC-compatible value routed via the SPI port to the appropriate D/A converter

- an SPI Atlas bus-compatible bi-directional amplifier interface

When an axis is configured for step motor control, the IO chip generates the pulse and direction signals.

Axis position information returns to the motion control IC in the form of encoder feedback using either the incremental encoder input signals, or via the bus as parallel word input.

The MC58x20 can co-exist in a CANOpen network as a slave device. It is CAN 2.0B compliant.

This page intentionally left blank.

## **3. Electrical Characteristics**

3

### In This Chapter

DC Characteristics for 58110, 58x20 CP

- DC Characteristics for 58x20 IO

- AC Characteristics

## 3.1 DC Characteristics for 58110, 58x20 CP

(Vcc and Ta per operating ratings,  $F_{clk} = 20.0 \text{ MHz}$ )

| Symbol    | Parameter                                                                                                                                                          | Minimum | Maximum           | Conditions                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|---------------------------|

| Vcc       | Supply Voltage                                                                                                                                                     | 3.0V    | 3.6V              |                           |

| ldd       | Supply Current                                                                                                                                                     |         | I20 mA            | All I/O pins are floating |

| Ta        | Operating free-air temperature                                                                                                                                     | -40°C   | 85°C              |                           |

| Input Vol | tages                                                                                                                                                              |         |                   |                           |

| Vih       | Logic I input voltage                                                                                                                                              | 2.0V    | Vcc + 0.3V        |                           |

| Vil       | Logic 0 input voltage                                                                                                                                              | 0       | 0.8V              |                           |

| Output V  | oltages                                                                                                                                                            |         |                   |                           |

| Voh       | Logic I Output Voltage                                                                                                                                             | 2.4V    |                   | lo = -2 mA                |

| Vol       | Logic 0 Output Voltage                                                                                                                                             |         | 0.4V              | lo = 2 mA                 |

| Other     |                                                                                                                                                                    |         |                   |                           |

| lout      | Tri-State output leakage current                                                                                                                                   | -2 μA   | 2 μΑ              | Vin = 0 or Vcc            |

| lin       | Input current                                                                                                                                                      | -30 μA  | 30 μ <b>Α</b>     |                           |

| Cio       | Input/Output capacitance                                                                                                                                           |         | 2/3 pF            | typical                   |

| Analog In | put                                                                                                                                                                |         |                   |                           |

| Zai       | Analog input source impedance                                                                                                                                      |         | l.4 kΩ            |                           |

| la        | Analog supply current                                                                                                                                              |         | 22 mA             |                           |

| Irefhi    | Vrefhi input current                                                                                                                                               |         | I.5 mA            |                           |

| Cai       | Analog input capacitance                                                                                                                                           |         | 30 <sub>P</sub> F | typical                   |

| Ezo       | Zero-offset error                                                                                                                                                  |         | ±2 LSB            | typical                   |

| Ednl      | Differential nonlinearity error.<br>Difference between the step width<br>and the ideal value.                                                                      |         | ±2 LSB            |                           |

| Einl      | Integral nonlinearity error.<br>Maximum deviation from the best<br>straight line through the ADC<br>transfer characteristics, excluding<br>the quantization error. |         | ±2 LSB            |                           |

## 3.2 DC Characteristics for 58x20 IO

(Vcc and Ta per operating ratings, Fclk = 40.0 MHz)

| Symbol    | Parameter                        | Minimum | Maximum | Conditions                |

|-----------|----------------------------------|---------|---------|---------------------------|

| Vcc       | Supply Voltage                   | 3.0V    | 3.6V    |                           |

| ldd       | Supply Current                   |         | 24 mA   | All I/O pins are floating |

| Та        | Operating free-air temperature   | -40°C   | 85°C    |                           |

| Input Vol | tages                            |         |         |                           |

| Vih       | Logic I input voltage            | 2.0V    | Vcc     |                           |

| Vil       | Logic 0 input voltage            | 0       | 0.8V    |                           |

| Output V  | oltages                          |         |         |                           |

| Voh       | Logic I Output Voltage           | 2.4V    |         | lo = -2 mA                |

| Vol       | Logic 0 Output Voltage           |         | 0.4V    | lo = 6 mA                 |

| Other     |                                  |         |         |                           |

| lout      | Tri-State output leakage current | -10 μA  | Ι0 μΑ   |                           |

| lin       | Input current                    | -10 μA  | Ι0 μΑ   |                           |

| Cio       | Input/Output capacitance         |         | 7/7 pF  | typical                   |

## 3.3 AC Characteristics

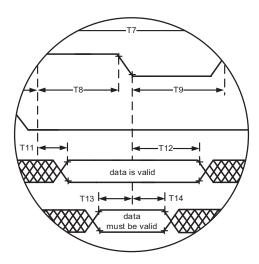

See timing diagrams in <u>Chapter 4, "I/O Timing Diagrams,"</u> for *Tn* numbers. The symbol "~" indicates active low signal.

| Timing Interval                                          | Tn  | Minimum  | Maximum  |

|----------------------------------------------------------|-----|----------|----------|

| Clock                                                    |     |          |          |

| IOClkIn Frequency (Fclk)                                 |     | 8 MHz    | 40 MHz   |

| IOClkIn pulse duration <sup>3</sup>                      | Tla | 0.4 T2a  | 0.6 T2a  |

| IOCIkIn Period                                           | T2a | 25 nsec  | 125 nsec |

| CPClkIn Frequency (Fclk) <sup>I</sup>                    |     | 4 MHz    | 20 MHz   |

| CPClkIn pulse duration <sup>3</sup>                      | TIb | 0.4 T2b  | 0.6 T2b  |

| CPClkIn Period                                           | T2b | 50 nsec  | 250 nsec |

| CPClkIn rise/fall time                                   | T58 |          | 5 nsec   |

| Encoder                                                  |     |          |          |

| Encoder Pulse Width                                      | Т3  | 200 nsec |          |

| Dwell Time Per State                                     | T4  | 100 nsec |          |

| Index Setup and Hold (relative to Quad A and Quad B low) | T5  | 0 nsec   |          |

| Host IO                                                  |     |          |          |

| ~HostSlct Hold Time                                      | T6  | 0 nsec   |          |

| ~HostSlct Setup Time                                     | T7  | 0 nsec   |          |

| HostCmd Setup Time                                       | T8  | 0 nsec   |          |

| HostCmd Hold Time                                        | Т9  | 0 nsec   |          |

| Read Data Access Time                                    | T10 |          | 25 nsec  |

| Read Data Hold Time                                      | TH  |          | 10 nsec  |

| ~HostRead High to HI-Z Time                              | TI2 |          | 20 nsec  |

| HostRdy Hold Time                                        | TI3 | 40 nsec  | 70 nsec  |

| ~HostWrite Pulse Width                                   | TI4 | 70 nsec  |          |

| Write Data Delay Time                                    | T15 |          | 15 nsec  |

| Write Data Hold Time                                     | TI6 | 0 nsec   |          |

| Read Recovery Time <sup>2</sup>                          | T17 | 60 nsec  |          |

| Write Recovery Time <sup>2</sup> T18         60 nsec           HostRead Pulse Width         T19         70 nsec           External Memory Read         CockOut low to control valid         T20         4 nsec           ClockOut low to address valid         T21         8 nsec         4 nsec           Address valid to -ReadEnable low         T23         5 nsec         CockOut low to -ReadEnable low         T23         8 nsec           Data access time from Address valid         T24         40 nsec         2 nsec         1 nsec           Data access time from Address valid         T24         40 nsec         2 nsec         2 nsec           Data access time from Address valid         T25         3 nsec         3 nsec         2 nsec           Data access time from Address inalid         T26         0 nsec         -         -           ReadEnable high         T36         0 nsec         -         -           ClockOut low to Strobe low         T29         5 nsec         CockOut low to Strobe low         T31         5 nsec           ClockOut high to control valid         T32         4 nsec         -         -         -           ClockOut low to Strobe low         T31         5 nsec         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Timing Interval                           | Tn          | Minimum     | Maximum    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------|-------------|------------|

| -HostRead Pulse Width       T19       70 nsec         External Memory Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | · · · · ·                                 | T18         | 60 nsec     |            |

| External Memory Read       Image: ClockOut low to control valid       T20       4 nsec         ClockOut low to control valid       T21       8 nsec         Address valid to -ReadEnable low       T22       5.5 nsec         ClockOut low to -ReadEnable low       T23       5 nsec         ClockOut low to -ReadEnable low       T23       -8 nsec       1 nsec         Data access time from Address valid       T24       40 nsec       40 nsec         Data access time from Address valid       T25       31 nsec       Data secup time before -ReadEnable high       T26       0 nsec         Data hold time after -ReadEnable high       T26       0 nsec       ClockOut low to control inactive       T27       5 nsec         ClockOut low to strobe low       T29       5 nsec       ClockOut low to Strobe low       T29       5 nsec         ClockOut low to Strobe low       T31       5 nsec       ClockOut high to control valid       T32       4 nsec         ClockOut high to control valid       T32       4 nsec       ClockOut high to adverse valid       T33       10 nsec         ClockOut high to control valid       T33       10 nsec       Adverse hold time after ClockOut low       T34       3.5 nsec         ClockOut high to control valid       T35       6 nsec       ClockOut low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | · · · · · · · · · · · · · · · · · · ·     | Т19         | 70 nsec     |            |

| ClockOut low to control valid       T20       4 nsec         ClockOut tow to address valid       T21       8 nsec         Address valid to -ReadEnable low       T22       5.5 nsec         ClockOut high to -ReadEnable low       T23       5 nsec         Data access time from Address valid       T24       40 nsec         Data access time from -ReadEnable high       T25       31 nsec         Data access time from -ReadEnable high       T25       8 nsec         Data access time from -ReadEnable high       T26       0 nsec         -ReadEnable high to Address valid       T26       0 nsec         ClockOut low to control inactive       T27       5 nsec         ClockOut low to strobe high       T30       6 nsec         ClockOut low to Strobe high       T30       6 nsec         W/-R low to R-W rising delay time       T31       5 nsec         ClockOut high to control valid       T32       4 nsec         ClockOut high to control valid       T33       10 nsec         Address valid to -WriteEnable low       T35       6 nsec         ClockOut high to control valid       T33       10 nsec         Address valid to -WriteEnable low       T36       33 nsec         Data hold time after -WriteEnable high       T36 <td></td> <td>,</td> <td>7011566</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | ,           | 7011566     |            |

| ClockOut low to address valid       T21       8 nsec         Address valid to -ReadEnable low       T23       5 nsec         ClockOut high to -ReadEnable low       T23       5 nsec         Data access time from Address valid       T24       40 nsec         Data access time from ReadEnable low       T25       31 nsec         Data secup time before -ReadEnable high       T26       0 nsec         Data secup time before -ReadEnable high       T26       0 nsec         ClockOut low to control inactive       T27       5 nsec         ClockOut low to strobe low       T29       5 nsec         ClockOut low to Strobe low       T29       5 nsec         ClockOut low to Strobe high       T30       6 nsec         ClockOut high to address valid       T31       5 nsec         ClockOut high to address valid       T33       10 nsec         ClockOut high to address valid       T34       3.5 nsec         ClockOut high to address valid       T33       10 nsec         Data sudriven from ClockOut low       T34       3.5 nsec<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | T20         |             | 4 nsec     |

| Address valid to -ReadEnable low     T22     5.5 nsec       ClockOut ligh to -ReadEnable low     T23     5 nsec       ClockOut low to -ReadEnable low     T23     8 nsec       Data access time from Address valid     T24     40 nsec       Data access time from Address valid     T25     31 nsec       Data secting marker -ReadEnable ligh     T25     0 nsec      ReadEnable high     T26     0 nsec      ReadEnable high to Address invalid     T26a     0 nsec      ReadEnable high to Address invalid     T26a     0 nsec       ClockOut low to control inactive     T27     5 nsec       Address hold time after -ReadEnable high     T30     6 nsec       ClockOut low to Strobe high     T30     6 nsec       Wi-R low to RI-W trising delay time     T31     5 nsec       ClockOut low to Strobe high     T33     10 nsec       Address valid to -WriteEnable low     T34     3.5 nsec       ClockOut low to -WriteEnable low     T33     6 nsec       ClockOut low to -WriteEnable low     T34     3.5 nsec       ClockOut low to -WriteEnable low     T37     -3 nsec       ClockOut low to -WriteEnable low     T37     -3 nsec       Data bus driven from ClockOut low     T41     6 nsec       Data sub driven from ClockOut low     T40<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |             |             |            |

| ClockOut high to -ReadEnable high         T23         5 nsec           ClockOut low to -ReadEnable high         T24         40 nsec           Data access time from Address valid         T24         40 nsec           Data access time from -ReadEnable high         T25         31 nsec           Data access time from -ReadEnable high         T26         0 nsec          ReadEnable high to Address invalid         T26a         0 nsec           ClockOut tow to control inactive         T27         5 nsec           ClockOut tow to control inactive         T27         5 nsec           ClockOut tow to Scrobe high         T30         6 nsec           W/-R low to Strobe high         T30         6 nsec           W/-R low to R/-W rising delay time         T31         5 nsec           ClockOut wor to Scrobe high         T33         10 nsec           ClockOut high to address valid         T33         6 nsec           ClockOut high to address valid         T35         6 nsec           ClockOut low to -WriteEnable low         T38         2 nsec           ClockOut low to -WriteEnable high         T36         31 nsec           Data setup time before -WriteEnable high         T38         2 nsec           ClockOut low to WriteEnable high         T38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |             | 5 5 nsec    | U HISCE    |

| ClockOut low to -ReadEnable high       T23a       -8 nsec       I nsec         Data access time from Address valid       T24       40 nsec         Data access time from ReadEnable low       T25       31 nsec         Data setup time before -ReadEnable high       T26a       0 nsec         -ReadEnable high to Address invalid       T26a       0 nsec         -ReadEnable high to Address invalid       T26a       0 nsec         ClockOut tow to control inactive       T27       5 nsec         ClockOut tow to control inactive       T27       5 nsec         ClockOut tow to control inactive       T30       6 nsec         W/-R low to R-WY rising delay time       T31       5 nsec         ClockOut high to address valid       T33       10 nsec         ClockOut high to address valid       T33       10 nsec         ClockOut high to address valid       T33       6 nsec         ClockOut high to address valid       T34       3.5 nsec         ClockOut high to address valid       T35       6 nsec         ClockOut high to address valid       T37       -3 nsec         Data sub griven from ClockOut low       T37       -3 nsec         Data sub griven from ClockOut low       T38       2 nsec         ClockOut high to control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |             |             | 5 nsec     |